# 82559 Fast Ethernet\* Multifunction PCI/ CardBus Controller

Networking Silicon

**int**<sub>a</sub>

### **Product Features**

- Optimum Integration for Lowest Cost Solution

- —Integrated IEEE 802.3 10BASE-T and 100BASE-TX compatible PHY

- -Glueless 32-bit PCI master interface

- -Glueless CardBus master interface

- Modem interface for combination solutions in PCI, CardBus, and MiniPCI designs

- -PXE Support in Combo Designs

- -128 Kbyte Flash interface

- -Integrated power management functions

- —Thin BGA 15mm<sup>2</sup> package

- Wired for Management and Reduced Total Cost of Ownership

- -Wired for Management support

- ----System Management Bus support for Total Cost of Ownership support

- -Power management capabilities

- -ACPI and PCI Power Management standards compliance

- Wake on "interesting" packets and link status change support

- —Magic Packet\* support

- -Remote power up support

- High Performance Networking Functions

—Chained memory structure similar to the 82558, 82557, and 82596

- Improved dynamic transmit chaining with multiple priorities transmit queues

- -Backward compatible software to the 82558 and 82557

- —Full Duplex support at both 10 and 100 Mbps

- -IEEE 802.3u Auto-Negotiation support

- 3 Kbyte transmit and 3 Kbyte receive FIFOs

- -Fast back-to-back transmission support with minimum interframe spacing

- —IEEE 802.3x 100BASE-TX Flow Control support

- -Adaptive Technology

- -TCP/UDP checksum offload capabilities

- Low Power Features

- -Low power 3.3 V device

- -Efficient dynamic standby mode

- -Deep power down support

- -Clockrun protocol support

### Datasheet

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The 82559 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1999

\* Third-party brands and names are the property of their respective owners.

# int<sub>el®</sub> Contents

| 1.0 | Introd                                 | luction                                                                                                                                                                                                                                                                                                          | 1                                      |

|-----|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|     | 1.1<br>1.2<br>1.3                      | 82559 Overview<br>Features, Enhancements, and Changes to the 82559 from the 82558<br>Enhancements to the 82559 C-Step                                                                                                                                                                                            | 1                                      |

| 2.0 | 82559                                  | 9 Architectural Overview                                                                                                                                                                                                                                                                                         | 3                                      |

|     | 2.1<br>2.2<br>2.3<br>2.4               | Parallel Subsystem Overview<br>FIFO Subsystem Overview<br>10/100 Mbps Serial CSMA/CD Unit Overview<br>10/100 Mbps Physical Layer Unit                                                                                                                                                                            | 4<br>5                                 |

| 3.0 | Signa                                  | I Descriptions                                                                                                                                                                                                                                                                                                   | 7                                      |

|     | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6 | Signal Type Definitions<br>PCI Bus and CardBus Interface Signals<br>3.2.1 Address and Data Signals<br>3.2.2 Interface Control Signals<br>3.2.3 System and Power Management Signals<br>Local Memory Interface Signals<br>System Management Bus (SMB) Interface Signals<br>Testability Port Signals<br>PHY Signals | 7<br>7<br>8<br>9<br>9<br>9<br>12<br>12 |

| 4.0 | 82559                                  | 9 Media Access Control Functional Description                                                                                                                                                                                                                                                                    | 15                                     |

|     | 4.1                                    | 82559 Initialization<br>4.1.1 Initialization Effects on 82559 Units<br>4.1.2 Initialization Effects on TCO Functionality                                                                                                                                                                                         | 15<br>15                               |

|     | 4.2                                    | PCI and CardBus Interface<br>4.2.1 82559 Bus Operations<br>4.2.2 PCI Mode Pin<br>4.2.3 Clockrun Signal                                                                                                                                                                                                           | 16<br>16<br>25<br>25                   |

|     | 4.3                                    | <ul> <li>4.2.4 Power Management Event and Card Status Change Signals</li> <li>PCI Power Management</li></ul>                                                                                                                                                                                                     | 26<br>26                               |

|     | 4.4                                    | CardBus Power Management                                                                                                                                                                                                                                                                                         |                                        |

|     | 4.5                                    | Wake on LAN (Preboot Wake-up)                                                                                                                                                                                                                                                                                    | 32                                     |

|     | 4.6                                    | Parallel Flash/Modem Interface                                                                                                                                                                                                                                                                                   |                                        |

|     | 4.7                                    | Serial EEPROM Interface                                                                                                                                                                                                                                                                                          |                                        |

|     | 4.8<br>4.9                             | 10/100 Mbps CSMA/CD Unit                                                                                                                                                                                                                                                                                         | 37<br>37<br>37<br>38                   |

| 5.0 |                                        |                                                                                                                                                                                                                                                                                                                  |                                        |

| 5.0 | 82558<br>5.1                           | Physical Layer Functional Description<br>100BASE-TX PHY Unit                                                                                                                                                                                                                                                     |                                        |

|     |       | 5.1.1 100BASE-TX Transmit Clock Generation                    |    |

|-----|-------|---------------------------------------------------------------|----|

|     |       | 5.1.2 100BASE-TX Transmit Blocks                              |    |

|     |       | 5.1.3 100BASE-TX Receive Blocks                               |    |

|     |       | 5.1.4 100BASE-TX Collision Detection                          |    |

|     |       | 5.1.5 100BASE-TX Link Integrity and Auto-Negotiation Solution |    |

|     | 5.0   | 5.1.6 Auto 10/100 Mbps Speed Selection                        |    |

|     | 5.2   | 10BASE-T Functionality                                        |    |

|     |       | 5.2.1 10BASE-T Transmit Clock Generation                      |    |

|     |       | 5.2.2 10BASE-T Transmit Blocks                                |    |

|     |       | 5.2.3 10BASE-T Receive Blocks                                 |    |

|     |       | 5.2.4 10BASE-T Collision Detection                            |    |

|     |       | 5.2.5 10BASE-T Link Integrity                                 |    |

|     |       | 5.2.6 10BASE-T Jabber Control Function                        |    |

|     | - 0   | 5.2.7 10BASE-T Full Duplex                                    |    |

|     | 5.3   | Auto-Negotiation Functionality                                |    |

|     |       | 5.3.1 Description                                             |    |

|     | - 4   | 5.3.2 Parallel Detect and Auto-Negotiation                    |    |

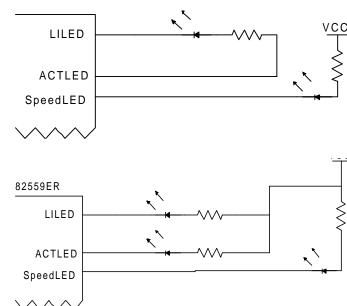

|     | 5.4   | LED Description                                               | 47 |

| 6.0 | 82559 | 9 Modem Functionality                                         |    |

|     | 6.1   | PCI Address Mapping to the Modem                              |    |

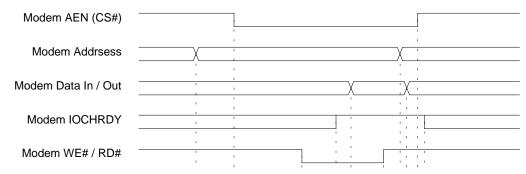

|     | 6.2   | Modem Read and Write Cycles                                   |    |

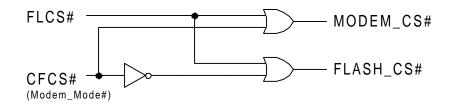

|     | 6.3   | Modem and Preboot eXtension Environment Coexistence           |    |

|     |       | 6.3.1 Programming Details                                     |    |

|     |       | 6.3.2 Support Circuitry                                       |    |

| 7.0 | 82559 | 9 TCO Functionality                                           |    |

|     | 7.1   | System Functionality with a TCO Controller                    | 51 |

|     | 7.2   | System Functionality without a TCO Controller                 |    |

|     | 7.2   | TCO Interface                                                 |    |

|     | 7.5   | 7.3.1 SMB Alert Signal (SMBALRT#)                             |    |

|     |       | 7.3.2 Alert Response Address (ARA) Cycle                      |    |

| 8.0 |       | nd CardBus Configuration Registers                            |    |

| 0.0 |       |                                                               |    |

|     | 8.1   | Function 0: LAN (Ethernet) PCI Configuration Space            |    |

|     |       | 8.1.1 PCI Vendor ID and Device ID Registers                   |    |

|     |       | 8.1.2 PCI Command Register                                    |    |

|     |       | 8.1.3 PCI Status Register                                     |    |

|     |       | 8.1.4 PCI Revision ID Register                                |    |

|     |       | 8.1.5 PCI Class Code Register                                 |    |

|     |       | 8.1.6 PCI Cache Line Size Register                            |    |

|     |       | 8.1.7 PCI Latency Timer                                       |    |

|     |       | 8.1.8 PCI Header Type                                         |    |

|     |       | 8.1.9 PCI Base Address Registers                              |    |

|     |       | 8.1.10 Base Address Registry Summary                          |    |

|     |       | 8.1.11 CardBus Card Information Structure (CIS) Pointer       |    |

|     |       | 8.1.12 PCI Subsystem Vendor ID and Subsystem ID Registers     |    |

|     |       | 8.1.13 Capability Pointer                                     |    |

|     |       | 8.1.14 Interrupt Line Register                                |    |

|     |       | 8.1.15 Interrupt Pin Register                                 |    |

|     |       | 8.1.16 Minimum Grant Register                                 | 62 |

|     |       |                                                               |    |

|      |        |         | Maximum Latency Register                         |    |

|------|--------|---------|--------------------------------------------------|----|

|      |        |         | Capability ID Register                           |    |

|      |        |         | Next Item Pointer                                |    |

|      |        | 8.1.20  | Power Management Capabilities Register           | 63 |

|      |        | 8.1.21  | Power Management Control/Status Register (PMCSR) | 64 |

|      |        |         | Data Register                                    |    |

|      | 8.2    | Functio | on 1: Modem PCI Configuration Space              | 66 |

|      |        | 8.2.1   | Modem Configuration ID Register                  | 66 |

|      |        | 8.2.2   | Modem Command Register                           | 67 |

|      |        | 8.2.3   | Modem Status Register                            | 67 |

|      |        | 8.2.4   | Modem Revision ID Register                       | 68 |

|      |        | 8.2.5   | Modem Header Type Register                       |    |

|      |        | 8.2.6   | Modem I/O Base Address Register                  |    |

|      |        | 8.2.7   | Modem Memory Base Address Register               |    |

|      |        | 8.2.8   | Modem CardBus CIS Pointer                        |    |

|      |        | 8.2.9   | Modem Subsystem Vendor ID Register               |    |

|      |        | 8.2.10  | Modem Subsystem ID Register                      |    |

|      |        | 8.2.11  | Modem Capabilities Pointer                       |    |

|      |        | 8.2.12  |                                                  |    |

|      |        | 8.2.13  | 1 5                                              |    |

|      |        |         | Modem Power Management Control/Status Register   |    |

|      |        | 8.2.15  | •                                                |    |

|      |        | 8.2.16  | Modem Support in PCI Mode                        |    |

| 9.0  | Contro |         | Registers                                        |    |

|      | 9.1    |         | thernet) Control/Status Registers                |    |

|      | 9.1    | 9.1.1   | System Control Block Status Word                 |    |

|      |        | 9.1.1   | System Control Block Command Word                |    |

|      |        | 9.1.2   | System Control Block General Pointer             |    |

|      |        | 9.1.3   | PORT                                             |    |

|      |        | 9.1.4   | Flash Control Register                           |    |

|      |        | 9.1.5   | EEPROM Control Register                          |    |

|      |        | 9.1.0   | Management Data Interface Control Register       |    |

|      |        | 9.1.7   | Receive Direct Memory Access Byte Count          |    |

|      |        | 9.1.8   | Early Receive Interrupt                          |    |

|      |        | 9.1.9   | Flow Control Register                            |    |

|      |        | 9.1.10  | Power Management Driver Register                 |    |

|      |        |         |                                                  |    |

|      |        | 9.1.12  | -                                                |    |

|      |        |         | General Status Register                          |    |

|      | 0.0    |         | Ethernet Card Status Change Registers            |    |

|      | 9.2    |         | cal Counters                                     |    |

|      | 9.3    |         | Control/Status Registers                         |    |

|      |        | 9.3.1   | Modem Base Memory Addressing                     |    |

|      |        | 9.3.2   | Modem Base I/O Addressing                        |    |

|      |        | 9.3.3   | Modem CardBus CSTCHG Registers                   |    |

| 10.0 |        | -       | sters                                            |    |

|      | 10.1   |         | egisters 0 - 7                                   |    |

|      |        |         | Register 0: Control Register Bit Definitions     |    |

|      |        | 10.1.2  | Register 1: Status Register Bit Definitions      | 86 |

|         | 10.1.3Register 2: PHY Identifier Register Bit Definitions8710.1.4Register 3: PHY Identifier Register Bit Definitions87                                    |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 10.1.5 Register 4: Auto-Negotiation Advertisement Register Bit Definitions87                                                                              |

|         | 10.1.6 Register 5: Auto-Negotiation Link Partner Ability Register Bit Definitions .<br>87                                                                 |

|         | 10.1.7 Register 6: Auto-Negotiation Expansion Register Bit Definitions88                                                                                  |

| 10.2    | MDI Registers 8 - 15                                                                                                                                      |

| 10.3    | MDI Register 16 - 31                                                                                                                                      |

|         | 10.3.1 Register 16: PHY Unit Status and Control Register Bit Definitions 88                                                                               |

|         | 10.3.2 Register 17: PHY Unit Special Control Bit Definitions                                                                                              |

|         | 10.3.3 Register 18: PHY Address Register90                                                                                                                |

|         | 10.3.4 Register 19: 100BASE-TX Receive False Carrier Counter Bit Definitions<br>90                                                                        |

|         | 10.3.5 Register 20: 100BASE-TX Receive Disconnect Counter Bit Definitions 90                                                                              |

|         | 10.3.6 Register 21: 100BASE-TX Receive Error Frame Counter Bit Definitions .<br>90                                                                        |

|         | 10.3.7 Register 22: Receive Symbol Error Counter Bit Definitions                                                                                          |

|         | 10.3.8 Register 23: 100BASE-TX Receive Premature End of Frame Error<br>Counter Bit Definitions 91                                                         |

|         | 10.3.9 Register 24: 10BASE-T Receive End of Frame Error Counter Bit Definitions<br>91                                                                     |

|         | 10.3.10 Register 25: 10BASE-T Transmit Jabber Detect Counter Bit Definitions<br>91                                                                        |

|         | 10.3.11 Register 26: Equalizer Control and Status Bit Definitions       91         10.3.12 Register 27: PHY Unit Special Control Bit Definitions       92 |

| 82559   | Test Port Functionality                                                                                                                                   |

| 11.1    | Introduction                                                                                                                                              |

| 11.2    | Asynchronous Test Mode93                                                                                                                                  |

| 11.3    | Test Function Description                                                                                                                                 |

|         | 11.3.1 Tristate93                                                                                                                                         |

|         | 11.3.2 NAND Tree                                                                                                                                          |

| Electri | cal and Timing Specifications97                                                                                                                           |

| 12.1    | Absolute Maximum Ratings97                                                                                                                                |

| 12.2    | DC Specifications97                                                                                                                                       |

| 12.3    | AC Specifications 101                                                                                                                                     |

| 12.4    | Timing Specifications                                                                                                                                     |

|         | 12.4.1 Clocks Specifications                                                                                                                              |

|         | 12.4.2 Timing Parameters                                                                                                                                  |

| Packa   | ge and Pinout Information                                                                                                                                 |

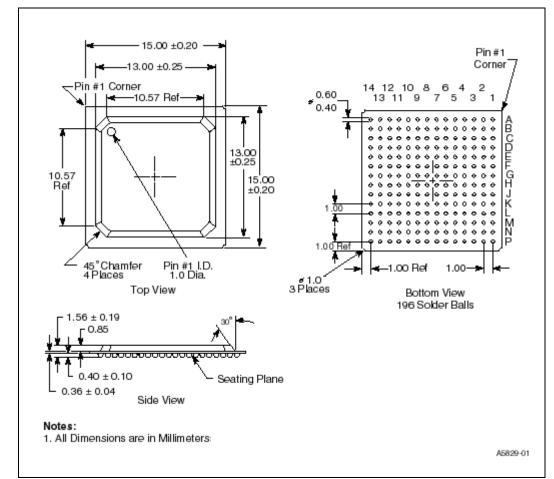

| 13.1    | Package Information111                                                                                                                                    |

| 13.2    | Pinout Information                                                                                                                                        |

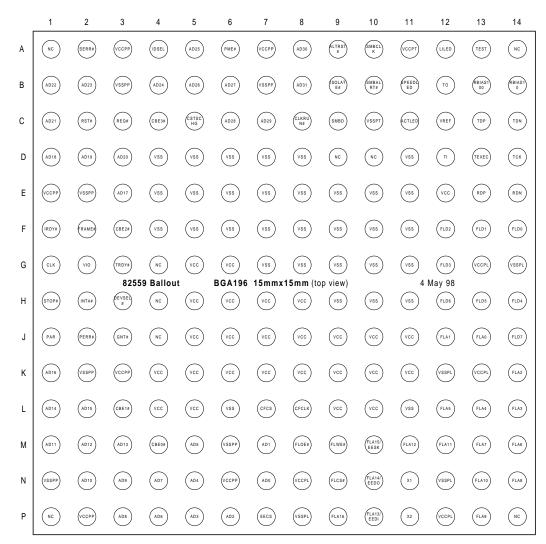

|         | 13.2.1 82559 Pin Assignments112                                                                                                                           |

|         | 13.2.2 82559 Ball Grid Array Diagram114                                                                                                                   |

# Figures

1

11.0

12.0

13.0

| 82559 Block Diagram | 3 |

|---------------------|---|

|---------------------|---|

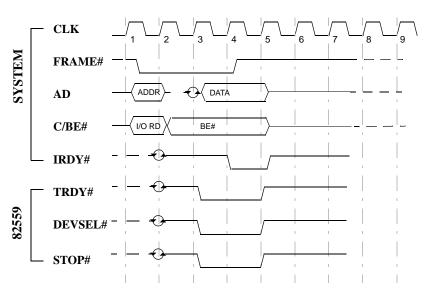

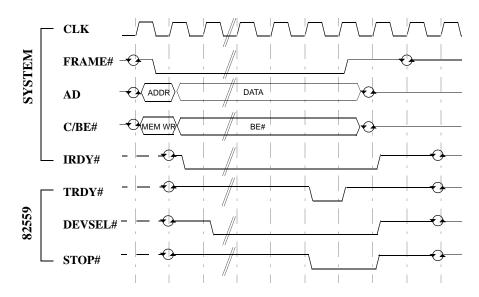

| 2  | Control/Status Register I/O Read Cycle           |     |

|----|--------------------------------------------------|-----|

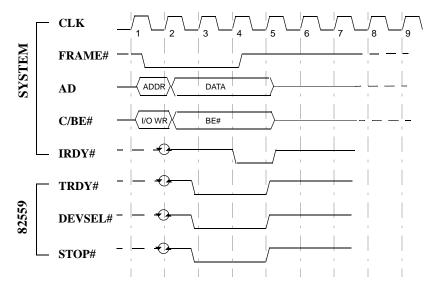

| 3  | Control/Status Register I/O Write Cycle          |     |

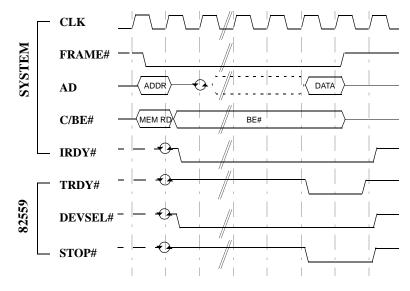

| 4  | Flash Buffer Read Cycle                          |     |

| 5  | Flash Buffer Write Cycle                         |     |

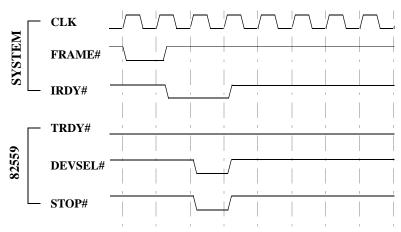

| 6  | PCI Retry Cycle                                  |     |

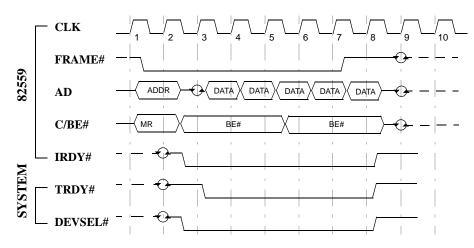

| 7  | Memory Read Burst Cycle                          |     |

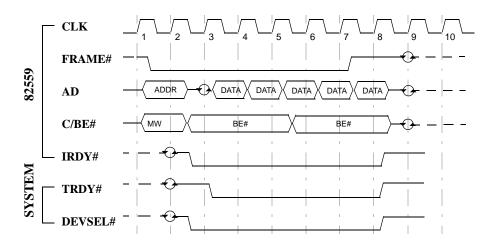

| 8  | Memory Write Burst Cycle                         |     |

| 9  | Isolate Signal Behavior to PCI Power Good Signal |     |

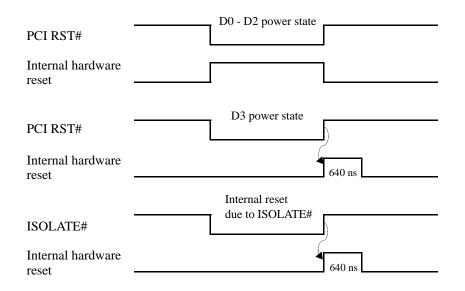

| 10 | 82559 Initialization Upon PCI RST# and ISOLATE#  |     |

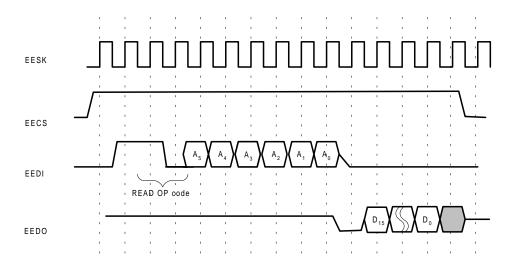

| 11 | 64-word EEPROM Read Instruction Waveform         |     |

| 12 | 82559 EEPROM Format                              |     |

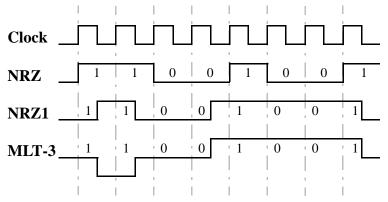

| 13 | NRZ to MLT-3 Encoding Diagram                    |     |

| 14 | Conceptual Transmit Differential Waveform        |     |

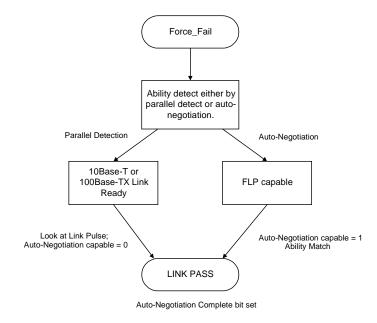

| 15 | Auto-Negotiation and Parallel Detect             |     |

| 16 | Two and Three LED Schematic Diagram              |     |

| 17 | Modem Read/Write Cycles                          |     |

| 18 | Support Circuitry Example                        |     |

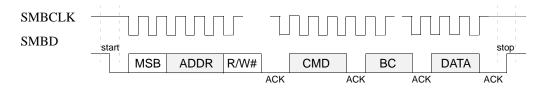

| 19 | SMB Session                                      |     |

| 20 | Slave Request for Data Transfer                  |     |

| 21 | PCI Configuration Registers                      |     |

| 22 | PCI Command Register                             |     |

| 23 | PCI Status Register                              |     |

| 24 | Cache Line Size Register                         |     |

| 25 | Base Address Register for Memory Mapping         |     |

| 26 | Base Address Register for I/O Mapping            |     |

| 27 | Modem PCI Configuration Registers                |     |

| 28 | 82559 Control/Status Register                    |     |

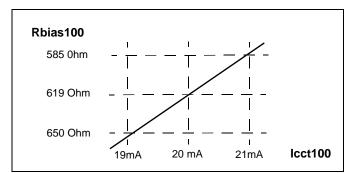

| 29 | RBIAS100 Resistance Versus Transmitter Current   |     |

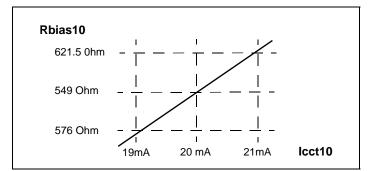

| 30 | RBIAS10 Resistance Versus Transmitter Current    |     |

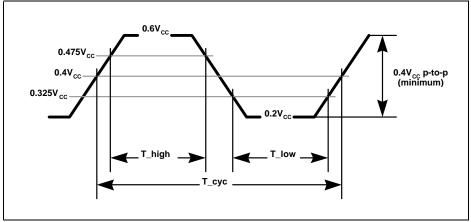

| 31 | PCI/CardBus Clock Waveform                       |     |

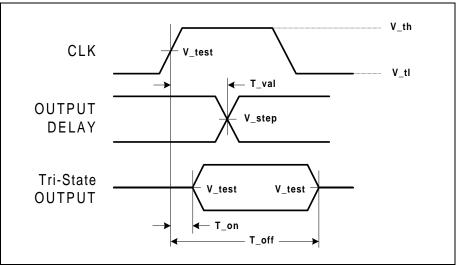

| 32 | Output Timing Measurement Conditions             |     |

| 33 | Input Timing Measurement Conditions              |     |

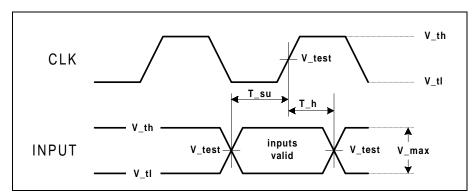

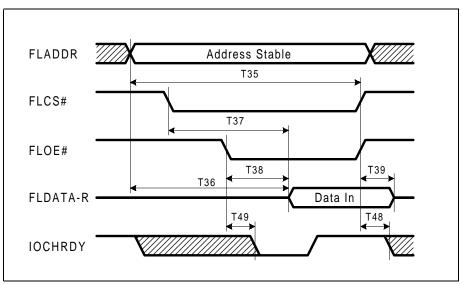

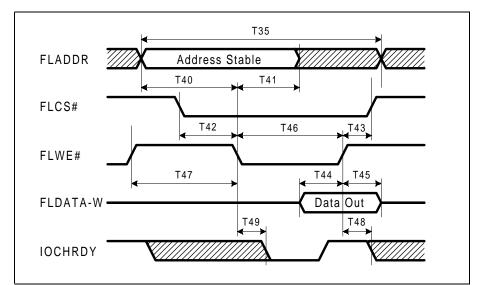

| 34 | Flash/Modem Timings for a Read Cycle             |     |

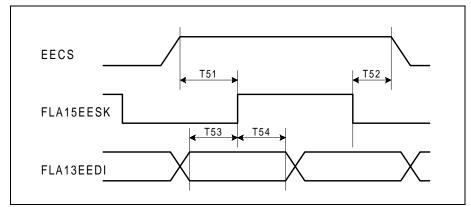

| 35 | Flash/Modem Timings for a Write Cycle            |     |

| 36 | EEPROM Timings                                   |     |

| 37 | 10BASE-T NLP Timings                             |     |

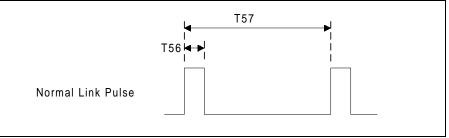

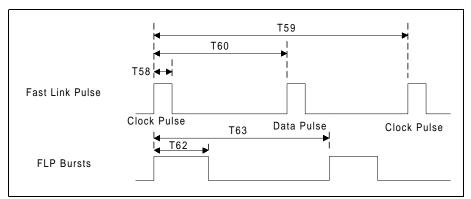

| 38 | Auto-Negotiation FLP Timings                     |     |

| 39 | Dimension Diagram for the 82559 196-pin BGA      |     |

| 40 | 82559 Ball Grid Array Diagram                    | 114 |

|    |                                                  |     |

# **Tables**

| 1 | EEPROM Words Field Descriptions       |  |

|---|---------------------------------------|--|

| 2 | 4B/5B Encoder                         |  |

| 3 | Magnetics Modules                     |  |

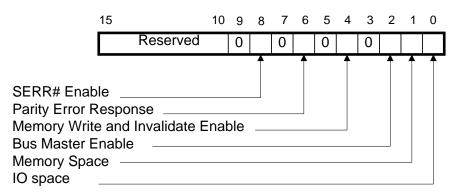

| 4 | PCI Command Register Bits             |  |

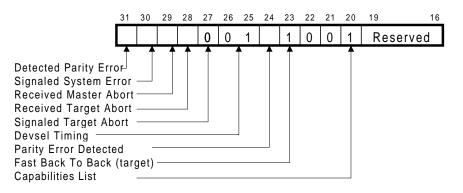

| 5 | PCI Status Register Bits              |  |

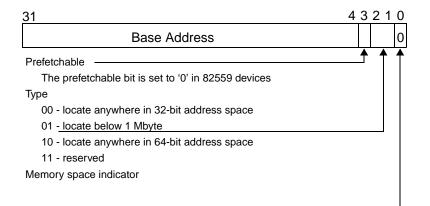

| 6 | Base Address Register Functionalities |  |

| 7 | 82559 ID Fields Programming           |  |

|   |                                       |  |

| 8  | Power Management Capability Register           | 63 |

|----|------------------------------------------------|----|

| 9  | Power Management Control and Status Register   | 64 |

| 10 | 82559 B-step Ethernet Data Register            | 64 |

| 11 | 82559 C-step Ethernet Data Register            | 65 |

| 12 | Power Management Control and Status Register   | 67 |

| 13 | Modem Status Register                          | 67 |

| 14 | Modem Revision Register                        | 68 |

| 15 | Ethernet Data Register                         | 69 |

| 16 | Power Management Driver Register               | 75 |

| 17 | General Control Register                       | 76 |

| 18 | General Status Register                        | 76 |

| 19 | LAN Function Event Register                    | 77 |

| 20 | LAN Function Event Mask Register               | 77 |

| 21 | LAN Function Present State Register            |    |

| 22 | LAN Force Event Register                       | 79 |

| 23 | 82558 Statistical Counters                     | 79 |

| 24 | Modem Function Event Mask Register             | 83 |

| 25 | Modem Function Present State Register          | 83 |

| 26 | NAND Tree Chains                               | 94 |

| 27 | General DC Specifications                      |    |

| 28 | PCI/CardBus Interface DC Specifications        | 97 |

| 29 | SMB Interface DC Specifications                | 98 |

| 30 | Flash/Modem/EEPROM Interface DC Specifications | 98 |

| 31 | LED Voltage/Current Characteristics            |    |

| 32 | 100BASE-TX Voltage/Current Characteristics     | 99 |

| 33 | 10BASE-T Voltage/Current Characteristics1      | 00 |

| 34 | AC Specifications for PCI Signaling1           | 01 |

| 35 | AC Specifications for CardBus Signaling1       | 01 |

| 36 | AC Specifications for Local Bus Signaling1     |    |

| 37 | PCI/CardBus Clock Specifications1              | 02 |

| 38 | X1 Clock Specifications1                       | 02 |

| 39 | Measure and Test Condition Parameters1         | 03 |

| 40 | PCI/CardBus Timing Parameters1                 | 04 |

| 41 | Flash Timing Parameters1                       | 05 |

| 42 | EEPROM Timing Parameters1                      | 07 |

| 43 | 10BASE-T NLP Timing Parameters1                | 80 |

| 44 | Auto-Negotiation FLP Timing Parameters1        | 80 |

| 45 | 100Base-TX Transmitter AC Specification1       | 09 |

| 46 | Flash Timing Parameters1                       | 09 |

| 47 | 82559 Pin Assignments1                         | 12 |

# **Revision History**

| Revision<br>Date | Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Jan. 1999        | 1.0      | First release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| May 1999         | 2.0      | <ul> <li>Preliminary 82559 C-step updates: <ul> <li>Added Section 1.3, "Enhancements to the 82559 C-Step"</li> <li>Changed resistance values for RBIAS pins in Section 3.6, "PHY Signals"</li> </ul> </li> <li>Changed signal names (Section 3.4, "System Management Bus (SMB) Interface Signals"): <ul> <li>Alert Bus Data: ALERTD (previously) to SMBD</li> <li>Alert Bus Clock: ALERTCLK (previously) to SMBCLK</li> <li>Bus Alert: BUSALRT (previously) to SMBALRT</li> </ul> </li> <li>Changed value of PCI power management in the Capability ID Register from 01H to 02H (Section 8.1.18, "Capability ID Register")</li> <li>Changed value of bits 18:16 in the Power Management Capabilities Register from 001b to 010b (Section 8.1.20, "Power Management Capabilities Register")</li> <li>Changed power consumption values in Table 15. Ethernet Data Register in Section 8.1.22, "Data Register"</li> <li>Changed name of Modem Capabilities Pointer (Modem Cap_Ptr) register in PCI Configuration space to Modem (Section 8.2, "Function 1: Modem PCI Configuration Space")</li> <li>Added Section 11.0, "82559 Test Port Functionality"</li> </ul> |

|                  |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

82559 — Networking Silicon

# intel

### 1.0 Introduction

### 1.1 82559 Overview

The 82559 is Intel's second generation fully integrated 10BASE-T/100BASE-TX LAN solution. The 82559 consists of both the Media Access Controller (MAC) and the physical layer (PHY) interface combined into a single component solution. The 82559 builds on the basic functionality of the 82558. In addition to the 82558, the 82559 has added new features and enhancements:

- Host-side CardBus interface

- Enhanced power management implementation

- Enhanced Total Cost of Ownership (TCO) support

- · Optimized Flash or modem interface support

The 32-bit PCI/CardBus controller provides enhanced scatter-gather bus mastering capabilities and enables the 82559 to perform high speed data transfers over the PCI bus and CardBus. Its bus master capabilities enable the component to process high level commands and perform multiple operations, which lowers CPU utilization by off-loading communication tasks from the CPU. Two large transmit and receive FIFOs of 3 Kbyte each help prevent data underruns and overruns while waiting for bus accesses. This enables the 82559 to transmit data with minimum interframe spacing (IFS).

The 82559 can operate in either full duplex or half duplex mode. In full duplex mode the 82559 adheres with the IEEE 802.3x Flow Control specification. Half duplex performance is enhanced by a proprietary collision reduction mechanism.

The 82559 includes a simple PHY interface to the wire transformer at rates of 10BASE-T and 100BASE-TX enables reduction in cost, real estate and design complexity. Its Auto-Negotiation capability for speed, duplex, and flow control mode reduces cost, real estate, and design complexity.

The 82559 also includes an interface to a serial (4-pin) EEPROM and a parallel interface to a 128 Kbyte Flash memory. The EEPROM provides power-on initialization for hardware and software configuration parameters. The parallel port can be used as either a Flash memory interface or an ISA-like interface for modem.

Combined with a Total Cost of Ownership (TCO) controller, the 82559 can help reduce the total cost of ownership in network environments. The device includes a System Management Bus (SMB) interface enabling the TCO controller to communicate with a management agent on the network.

# 1.2 Features, Enhancements, and Changes to the 82559 from the 82558

- Glueless 32-bit PCI bus master interface

- · Support for latchless Flash interface with up to 128 Kbyte of Flash addressing

- Glueless CardBus master interface

- Modem interface for combination solution (LAN and modem) in PCI and CardBus designs

- Low power consumption for LAN/modem combination designs to meet CardBus power requirements

- Compliance with Advanced Configuration and Power Interface and PCI Power Management specifications

- · Support for wake-up on interesting packets and link status change

- Support for remote power-up using Wake on LAN\* (WOL) technology

- Deep power-down mode support

- Support of Total Cost of Ownership (TCO) management interface and Wired for Management (WfM)

- Backward compatible software with 82558 and 82557

- TCP/UDP checksum offload capabilities

- Support for Intel's Adaptive Technology

The following is a list of changes that were made from the 82558 B-step Fast Ethernet Controller to the 82559 Fast Ethernet Multifunction PCI/CardBusController.

- Use of 3.3 V power supply (82559) versus 5 V power supply

- Individual Address, Multicast Address, and ARP wake-up events merged into extended programmable wake-up packet command and removed from the CSMA command

- · Receive collision bit in the RFD status word replaced with a TCO indication bit

- SMB port implemented to support TCO management interface

- PHY identifier in MII Register 3 modified

- External PHY support removed

- PHY-based flow control removed (802.3x flow control was not removed)

#### 1.3 Enhancements to the 82559 C-Step

The success of the 82559 B-step in mobile designs has spurred the addition of several new features to the device. These enhancements integrate new capabilities into the 82559 for both CardBus and MiniPCI system designs:

- · Reducing the declared Flash window requirement to 128 bytes from 1 Mbyte.

- Adding glueless support for PXE Flash ROM in LAN/modem combination designs by adding an external gating signal

## 2.0 82559 Architectural Overview

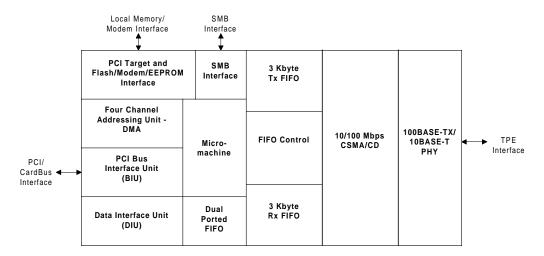

Figure 1 is a high level block diagram of the 82559. It is divided into five main subsystems: a parallel subsystem, a FIFO subsystem, the Total Cost of Ownership (TCO) subsystem, the 10/100 Mbps Carrier Sense Multiple Access with Collision Detect (CSMA/CD) unit, and the 10/100 Mbps physical layer (PHY) unit.

#### Figure 1. 82559 Block Diagram

### 2.1 Parallel Subsystem Overview

The parallel subsystem is broken down into several functional blocks: a PCI bus master interface, a micromachine processing unit and its corresponding microcode ROM, and a PCI Target Control/ Flash/EEPROM/Modem interface. The parallel subsystem also interfaces to the FIFO subsystem, passing data (such as transmit, receive, and configuration data) and command and status parameters between these two blocks.

The dual function LAN and modem interface provides a complete glueless connection to the PCI bus and is compliant with the PCI Bus Specification, Revision 2.2. The 82559 provides 32 bits of addressing and data, as well as the complete control interface to operate on a PCI bus. As a PCI target, it follows the PCI configuration format which allows all accesses to the 82559 to be automatically mapped into free memory and I/O space upon initialization of a PCI system. For processing of transmit and receive frames, the 82559 operates as a master on the PCI bus, initiating zero wait state transfers for accessing these data parameters.

The 82559 Control/Status Register Block is part of the PCI target element. The Control/Status Register block consists of the following 82559 internal control registers: System Control Block (SCB), PORT, Flash Control, EEPROM Control, Modem Control and Management Data Interface (MDI) Control.

The micromachine is an embedded processing unit contained in the 82559 that enables Adaptive Technology. The micromachine accesses the 82559 microcode ROM working its way through the operation codes, opcodes (or instructions), contained in the ROM to perform its functions. Parameters accessed from memory such as pointers to data buffers are also used by the

micromachine during the processing of transmit or receive frames by the 82559. A typical micromachine function is to transfer a data buffer pointer field to the 82559 DMA unit for direct access to the data buffer. The micromachine is divided into two units, Receive Unit and Command Unit which includes transmit functions. These two units operate independently and concurrently. Control is switched between the two units according to the microcode instruction flow. The independence of the Receive and Command units in the micromachine allows the 82559 to execute commands and receive incoming frames simultaneously, with no real-time CPU intervention.

The 82559 contains an interface to an external Flash memory, an external serial EEPROM, and modem. These three interfaces are multiplexed, and both read and write accesses are supported. The Flash may be used for remote boot functions, network statistical and diagnostics functions, and management functions. The Flash is mapped into host system memory (anywhere within the 32-bit memory address space) for software accesses. It is also mapped into an available boot expansion ROM location during boot time of the system. More information on the Flash interface is detailed in Section 4.6, "Parallel Flash/Modem Interface" on page 33. The EEPROM is used to store relevant information for a LAN connection such as node address, as well as board manufacturing and configuration information. Both read and write accesses to the EEPROM are supported by the 82559. Information on the EEPROM interface is detailed in Section 4.7, "Serial EEPROM Interface" on page 33. The modem interface uses an ISA-like signal and is described in more detail in Section 6.0, "82559 Modem Functionality" on page 49.

### 2.2 FIFO Subsystem Overview

The 82559 FIFO subsystem consists of a 3 Kbyte transmit FIFO and 3 Kbyte receive FIFO. Each FIFO is unidirectional and independent of the other. The FIFO subsystem serves as the interface between the 82559 parallel side and the serial CSMA/CD unit. It provides a temporary buffer storage area for frames as they are either being received or transmitted by the 82559, which improves performance:

- Transmit frames can be queued within the transmit FIFO, allowing back-to-back transmission within the minimum Interframe Spacing (IFS).

- The storage area in the FIFO allows the 82559 to withstand long PCI bus latencies without losing incoming data or corrupting outgoing data.

- The 82559 transmit FIFO threshold allows the transmit start threshold to be tuned to eliminate underruns while concurrent transmits are being performed.

- The FIFO subsection allows extended PCI zero wait state burst accesses to or from the 82559 for both transmit and receive frames since the transfer is to the FIFO storage area rather than directly to the serial link.

- Transmissions resulting in errors (collision detection or data underrun) are retransmitted directly from the 82559 FIFO, increasing performance and eliminating the need to re-access this data from the host system.

- Incoming runt receive frames (in other words, frames that are less than the legal minimum frame size) can be discarded automatically by the 82559 without transferring this faulty data to the host system.

### 2.3 10/100 Mbps Serial CSMA/CD Unit Overview

The CSMA/CD unit of the 82559 allows it to be connected to either a 10 or 100 Mbps Ethernet network. The CSMA/CD unit performs all of the functions of the 802.3 protocol such as frame formatting, frame stripping, collision handling, deferral to link traffic, etc. The CSMA/CD unit can also be placed in a full duplex mode which allows simultaneous transmission and reception of frames.

### 2.4 10/100 Mbps Physical Layer Unit

The Physical Layer (PHY) unit of the 82559 allows connection to either a 10 or 100 Mbps Ethernet network. The PHY unit supports Auto-Negotiation for 100BASE-TX Full Duplex, 100BASE-TX Half Duplex, 10BASE-T Full Duplex, and 10BASE-T Half Duplex. It also supports three LED pins to indicate link status, network activity, and speed.

82559 — Networking Silicon

# intel

# 3.0 Signal Descriptions

### 3.1 Signal Type Definitions

| Туре  | Name                | Description                                                                                                                                                                                                                                                                                                                                           |

|-------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN    | Input               | The input pin is a standard input only signal.                                                                                                                                                                                                                                                                                                        |

| OUT   | Output              | The output pin is a Totem Pole Output pin and is a standard active driver.                                                                                                                                                                                                                                                                            |

| T/S   | Tri-State           | The tri-state pin is a bidirectional, input/output pin.                                                                                                                                                                                                                                                                                               |

| S/T/S | Sustained Tri-State | The sustained tri-state pin is an active low tri-state signal owned<br>and driven by one agent at a time. The agent asserting the S/T/<br>S pin low must drive it high at least one clock cycle before<br>floating the pin. A new agent can only assert an S/T/S signal low<br>one clock cycle after it has been tri-stated by the previous<br>owner. |

| O/D   | Open Drain          | The open drain pin allows multiple devices to share this signal as a wired-OR.                                                                                                                                                                                                                                                                        |

| A/I   | Analog Input        | The analog input pin is used for analog input signals.                                                                                                                                                                                                                                                                                                |

| A/O   | Analog Output       | The analog output pin is used for analog output signals.                                                                                                                                                                                                                                                                                              |

| В     | Bias                | The bias pin is an input bias.                                                                                                                                                                                                                                                                                                                        |

### 3.2 PCI Bus and CardBus Interface Signals

### 3.2.1 Address and Data Signals

| Symbol     | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD[31:0]   | T/S  | Address and Data. The address and data lines are multiplexed on the same PCI pins. A bus transaction consists of an address phase followed by one or more data phases. During the address phase, the address and data lines contain the 32-bit physical address. For I/O, this is a byte address; for configuration and memory, it is a Dword address. The 82559 uses little-endian byte ordering (in other words, AD[31:24] contain the most significant byte and AD[7:0] contain the least significant byte). During the data phases, the address and data lines contain data. |

| C/BE[3:0]# | T/S  | <b>Command and Byte Enable.</b> The bus command and byte enable signals are multiplexed on the same PCI pins. During the address phase, the C/BE# lines define the bus command. During the data phase, the C/BE# lines are used as Byte Enables. The Byte Enables are valid for the entire data phase and determine which byte lanes carry meaningful data.                                                                                                                                                                                                                      |

| PAR        | T/S  | <b>Parity.</b> Parity is even across AD[31:0] and C/BE[3:0]# lines. It is stable<br>and valid one clock after the address phase. For data phases, PAR is<br>stable and valid one clock after either IRDY# is asserted on a write<br>transaction or TRDY# is asserted on a read transaction.Once PAR is<br>valid, it remains valid until one clock after the completion of the current<br>data phase. The master drives PAR for address and write data<br>phases; and the target, for read data phases.                                                                           |

### 3.2.2 Interface Control Signals

| Symbol  | Туре  | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FRAME#  | S/T/S | <b>Cycle Frame.</b> The cycle frame signal is driven by the current master to indicate the beginning and duration of a transaction. FRAME# is asserted to indicate the start of a transaction and de-asserted during the final data phase.                                                                                                                                                                                                                           |

| IRDY#   | S/T/S | <b>Initiator Ready.</b> The initiator ready signal indicates the bus master's ability to complete the current data phase and is used in conjunction with the target ready (TRDY#) signal. A data phase is completed on any clock cycle where both IRDY# and TRDY# are sampled asserted (low) simultaneously.                                                                                                                                                         |

| TRDY#   | S/T/S | <b>Target Ready.</b> The target ready signal indicates the selected device's ability to complete the current data phase and is used in conjunction with the initiator ready (IRDY#) signal. A data phase is completed on any clock cycle where both IRDY# and TRDY# are sampled asserted (low) simultaneously.                                                                                                                                                       |

| STOP#   | S/T/S | <b>Stop.</b> The stop signal is driven by the target to indicate to the initiator that it wishes to stop the current transaction. As a bus slave, STOP# is driven by the 82559 to inform the bus master to stop the current transaction. As a bus master, STOP# is received by the 82559 to stop the current transaction.                                                                                                                                            |

| IDSEL   | IN    | <b>Initialization Device Select.</b> The initialization device select signal is used by the 82559 as a chip select during PCI configuration read and write transactions. This signal is provided by the host in PCI systems. In a CardBus system, this pin should not be connected.                                                                                                                                                                                  |

| DEVSEL# | S/T/S | <b>Device Select.</b> The device select signal is asserted by the target once it has detected its address. As a bus master, the DEVSEL# is an input signal to the 82559 indicating whether any device on the bus has been selected. As a bus slave, the 82559 asserts DEVSEL# to indicate that it has decoded its address as the target of the current transaction.                                                                                                  |

| REQ#    | T/S   | <b>Request.</b> The request signal indicates to the bus arbiter that the 82559 desires use of the bus. This is a point-to-point signal and every bus master has its own REQ#.                                                                                                                                                                                                                                                                                        |

| GNT#    | IN    | <b>Grant.</b> The grant signal is asserted by the bus arbiter and indicates to the 82559 that access to the bus has been granted. This is a point-to-point signal and every master has its own GNT#.                                                                                                                                                                                                                                                                 |

| INTA#   | O/D   | <b>Interrupt A.</b> The interrupt A signal is used to request an interrupt by the 82559. This is an active low, level triggered interrupt signal.                                                                                                                                                                                                                                                                                                                    |

| SERR#   | O/D   | <b>System Error.</b> The system error signal is used to report address parity errors. When an error is detected, SERR# is driven low for a single PCI clock.                                                                                                                                                                                                                                                                                                         |

| PERR#   | S/T/S | <b>Parity Error.</b> The parity error signal is used to report data parity errors during all PCI transactions except a Special Cycle. The parity error pin is asserted two clock cycles after the error was detected by the device receiving data. The minimum duration of PERR# is one clock for each data phase where an error is detected. A device cannot report a parity error until it has claimed the access by asserting DEVSEL# and completed a data phase. |

### 3.2.3 System and Power Management Signals

intel

| Symbol                             | Туре          | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| CLK                                | IN            | <b>Clock.</b> The Clock signal provides the timing for all PCI transactions<br>and is an input signal to every PCI device. The 82559 requires a PCI<br>Clock signal (frequency greater than or equal to 16 MHz) for nominal<br>operation. The 82559 supports Clock signal suspension using the<br>Clockrun protocol.                                                                                                                                                      |  |  |  |  |  |

| CLKRUN#                            | IN/OUT<br>O/D | <b>Clockrun.</b> The Clockrun signal is used by the system to pause or slow down the PCI Clock signal. It is used by the 82559 to enable or disable suspension of the PCI Clock signal or restart of the PCI clock. When the Clockrun signal is not used, this pin should be connected to an external pull-down resistor.                                                                                                                                                 |  |  |  |  |  |

| RST#                               | IN            | <b>Reset.</b> The PCI Reset signal is used to place PCI registers, sequencers, and signals into a consistent state. When RST# is asserted, all PCI output signals will be tri-stated.                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| PME#<br>(PCI)                      | O/D           | <b>Power Management Event.</b> The Power Management Event signal indicates that a power management event has occurred in a PCI bus system.                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| CSTSCHG<br>(CardBus)/<br>WOL (PCI) | OUT           | <b>Card Status Change/Wake on LAN.</b> This pin is multiplexed to provide Card Status Change or Wake on LAN signals. In a CardBus system, it is used as the Card Status Change output signal and is an asynchronous signal to the Clock signal. It indicates that a power management event has occurred in a CardBus system. In a PCI system, it is used as the WOL pin and provides a positive pulse of approximately 52 ms upon detection of an incoming Magic Packet*. |  |  |  |  |  |

| ISOLATE#                           | IN            | <b>Isolate.</b> The Isolate signal is used to isolate the 82559 from the PCI bus. When Isolate is active (low), the 82559 does not drive its PCI outputs (except PME# and CSTSCHG) or sample its PCI inputs (including CLK and RST#). If the 82559 is not powered by an auxiliary power source, the ISOLATE# pin must be pulled high through a 10 K $\Omega$ resistor.                                                                                                    |  |  |  |  |  |

| ALTRST#                            | IN            | Alternate Reset. The Alternate Reset signal is used to reset the 82559 on power-up. In systems that support an auxiliary power supply, ALTRST# should be connected to a power-up detection circuit. Otherwise, ALTRST# should be tied to $V_{CC}$ .                                                                                                                                                                                                                       |  |  |  |  |  |

| VIO                                | B<br>IN       | <b>Voltage Input/Output.</b> The VIO pin is the voltage bias pin and is typically connected to +5 V in a PCI bus system and +3.3 V in a CardBus system.                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

### 3.3 Local Memory Interface Signals

| Symbol            | Туре | Name and Function                                                                                                                                                                                                                                                                     |  |  |  |

|-------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| FLD[7:0]          | T/S  | Flash/Modem Data Input/Output. These pins are used for Flash/<br>Modem data interface.                                                                                                                                                                                                |  |  |  |

| FLA[16]/<br>CLK25 | OUT  | Flash Address[16]/25 MHz Clock. This multiplexed pin is controlled<br>by the status of the Flash Address[7] (FLA[7]) pin. If FLA[7] is left<br>floating, this pin is used as FLA[16]; otherwise, if FLA[7] is connected<br>to a pull-up resistor, this pin is used as a 25 MHz clock. |  |  |  |

| FLA[15]/<br>EESK  | OUT  | Flash Address[15]/EEPROM Data Output. During Flash accesses, this multiplexed pin acts as the Flash Address [15] output signal. During EEPROM accesses, it acts as the serial shift clock output to the EEPROM.                                                                       |  |  |  |

| Туре       | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| IN/OUT     | Flash Address[14]/EEPROM Data Output. During Flash accesses,<br>this multiplexed pin acts as the Flash Address [14] output signal.<br>During EEPROM accesses, it acts as serial input data to the EEPROM<br>Data Output signal.                                                                                                                                                                                                              |  |  |  |  |  |

| OUT        | Flash Address[13]/EEPROM Data Input. During Flash accesses,<br>this multiplexed pin acts as the Flash Address [13] output signal.<br>During EEPROM accesses, it acts as serial output data to the<br>EEPROM Data Input signal.                                                                                                                                                                                                               |  |  |  |  |  |

| OUT<br>O/D | Flash Address[12]/Modem Central Site Mode. This multiplexed pin acts as the Flash Address[12] output signal in a non-modem card. If modem is enabled, it is used as an output signal to the modem. It is either floated by default or driven low by the Modem System Control Registers.                                                                                                                                                      |  |  |  |  |  |

| IN/OUT     | Flash Address[11]/Modem Interrupt. This multiplexed pin acts as the Flash Address[11] output signal in a non-modem card. If modem is enabled, it is used as the Modem Interrupt input signal.                                                                                                                                                                                                                                                |  |  |  |  |  |

| IN/OUT     | Flash Address[10]/Modem Ring. This multiplexed pin acts as the Flash Address[10] output signal in a non-modem card. If modem is enabled, it is used as the Modem Ring input signal.                                                                                                                                                                                                                                                          |  |  |  |  |  |

| OUT        | Flash Address[9]/Modem Reset. This multiplexed pin acts as the Flash Address[9] output signal in a non-modem card. If modem is enabled, it acts as the Modem Reset signal with an active high output                                                                                                                                                                                                                                         |  |  |  |  |  |

| IN/OUT     | Flash Address[8]/ISA Input/Output Channel Ready. This<br>multiplexed pin acts as the Flash Address[8] output signal in a non-<br>modem card. If modem is enabled, it is used as the ISA IOCHRDY<br>input signal.                                                                                                                                                                                                                             |  |  |  |  |  |

| T/S        | <b>Flash Address[7]/Clock Enable.</b> This is a multiplexed pin and acts as the Flash Address[7] output signal during nominal operation. Whe the PCI RST# signal is active, this pin acts as input control over the FLA[16]/CLK25 output signal. If the FLA[7]/CLKEN pin is connected t a pull-up resistor $(3.3 \text{ K}\Omega)$ , a 25 MHz clock signal is provided on the FLA[16]/CLK25 output; otherwise, it is used as FLA[16] output. |  |  |  |  |  |

| OUT        | Flash Address[6:2]. These pins are used as Flash address outputs to support 128 Kbyte Flash addressing. If the modem is enabled, these pins carry modem address bits 6:2.                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| T/S        | Flash Address[1]/Auxiliary Power. This multiplexed pin acts as the Flash Address[1] output signal during nominal operation. If the modem is enabled, this pin carries modem address bit 1. When RST is active (low), it acts as the power supply indicator. If the 82559 is fed PCI power, this pin should be connected to a pull-down resistor; if the 82559 is fed by auxiliary power, this pin should be connected to a pull-up resistor. |  |  |  |  |  |

| T/S        | <b>Flash Address [0]/PCI Mode.</b> This multiplexed pin acts as the Flash Address[0] output signal during nominal operation. If the modem is enabled, this pin carries modem address bit 0. When RST# is active (low), it acts as the input system type. If the 82559 is used in a CardBus system, this pin should be connected to a pull-up resistor ( $3.3 \text{ K}\Omega$ ); otherwise, the 82559 considers the host as a PCI system.    |  |  |  |  |  |

| OUT        | <b>EEPROM Chip Select.</b> The EEPROM Chip Select signal is used to assert chip select to the serial EEPROM.                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| OUT        | Flash Chip Select/Address Enable. The Flash Chip Select signal is active during Flash. In modem mode, it acts as an ISA-like Address Enable signal (modem chip select).                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|            | IN/OUT<br>OUT<br>OUT<br>O/D<br>IN/OUT<br>IN/OUT<br>IN/OUT<br>T/S<br>OUT<br>T/S<br>T/S                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Symbol | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| FLOE#  | OUT  | Flash Output Enable. This pin provides an active low output enable control (read) to the Flash memory. If the modem is enabled, this is a active-low output enable (read) of the modem.                                                                                                                                                                                                                                                                                              |  |  |  |  |

| FLWE#  | OUT  | lash Write Enable. This pin provides an active low write enable<br>ontrol to the Flash memory. If the modem is enabled, this is an active<br>w write-enable to the modem.                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| CFCS#  | OUT  | Security ASIC Chip Select. This pin provides an active low function<br>enable to enable/disable Flash memory in Combo designs. This signal<br>is asserted high to enable Flash memory in LAN/modem designs. If<br>this signal is asserted low, the modem device is enabled, and local bus<br>signals are defined for modem. This pin is controlled by setting/<br>clearing the Boot Enable bit in the BootROM BAR. This bit is set<br>following a PCI reset enabling external Flash. |  |  |  |  |