# Élan<sup>™</sup>SC520 Microcontroller User's Manual

Order #22004A

| © 1999 Advanced Micro Devices, Inc. All rights reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any inellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no iability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right. |

| AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Frademarks Trademarks Trademarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AMD, the AMD logo and combinations thereof, Am186, AMDebug, AMD Athlon, E86, K86, and Élan are trademarks; Am486 and Am5 <sub>x</sub> 86 are egistered trademarks; and FusionE86 is a service mark of Advanced Micro Devices, Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Microsoft, Windows, and Windows NT are registered trademarks of Microsoft Corp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### IF YOU HAVE QUESTIONS, WE'RE HERE TO HELP YOU.

The AMD customer service network includes U.S. offices, international offices, and a customer training center. Expert technical assistance is available from the AMD worldwide staff of field application engineers and factory support staff to answer E86™ family hardware and software development questions.

Frequently accessed numbers are listed below. Additional contact information is listed on the back of this manual. AMD's WWW site lists the latest phone numbers.

## **Technical Support**

Answers to technical questions are available online, through e-mail, and by telephone.

Go to AMD's home page at **www.amd.com** and follow the Service link for the latest AMD technical support phone numbers, software, and Frequently Asked Questions.

For technical support questions on all E86 products, send e-mail to **epd.support@amd.com** (in the US and Canada) or **euro.tech@amd.com** (in Europe and the UK).

You can also call the AMD Corporate Applications Hotline at:

(800) 222-9323 Toll-free for U.S. and Canada

44-(0) 1276-803-299 U.K. and Europe hotline

## **WWW Support**

For specific information on E86 products, access the AMD home page at **www.amd.com** and follow the Embedded Processors link. These pages provide information on upcoming product releases, overviews of existing products, information on product support and tools, and a list of technical documentation. Support tools include online benchmarking tools and CodeKit software—tested source code example applications. Many of the technical documents are available online in PDF form.

Questions, requests, and input concerning AMD's WWW pages can be sent via e-mail to **webmaster@amd.com**.

## **Documentation and Literature Support**

Data books, user's manuals, data sheets, application notes, and product CDs are free with a simple phone call. Internationally, contact your local AMD sales office for product literature.

To order literature, call:

(800) 222-9323 Toll-free for U.S. and Canada

(512) 602-5651 Direct dial worldwide

(512) 602-7639 Fax

#### **Third-Party Support**

AMD FusionE86<sup>SM</sup> program partners provide an array of products designed to meet critical time-to-market needs. Products and solutions available include emulators, hardware and software debuggers, board-level products, and software development tools, among others. The WWW site and the *E86<sup>TM</sup> Family Products Development Tools CD*, order# 21058, describe these solutions. In addition, mature development tools and applications for the x86 platform are widely available in the general marketplace.

## **TABLE OF CONTENTS**

| PREFACE   | INTRODUCTION Élan™SC520 Microcontroller Purpose of this Manual Intended Audience Overview of this Manual Related Documents AMD Documentation Additional Information Documentation Conventions                                                                                                                                                                                                                                                                                                                                                                                                   | xxii<br>xxiii<br>xxiii<br>xxiv<br>xxiv<br>xxiv                                                 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

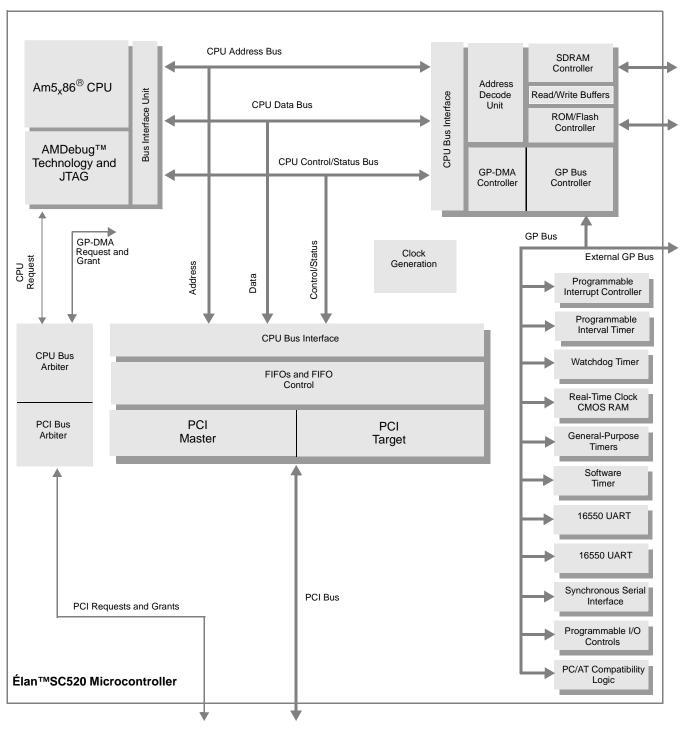

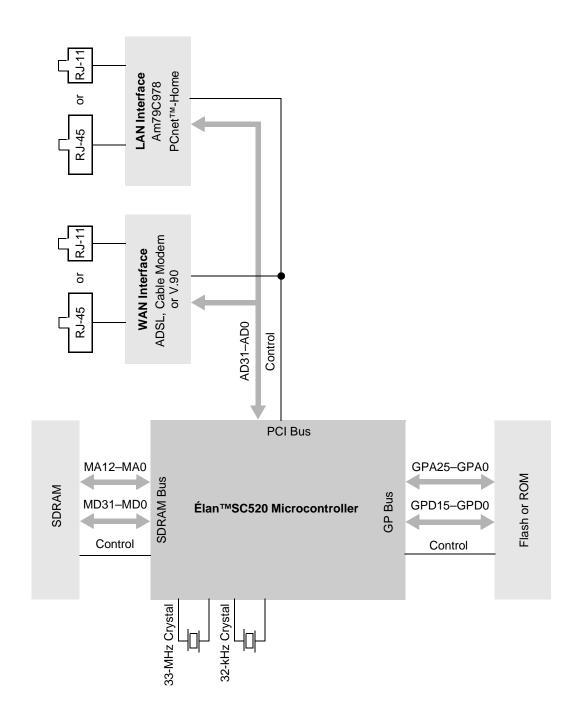

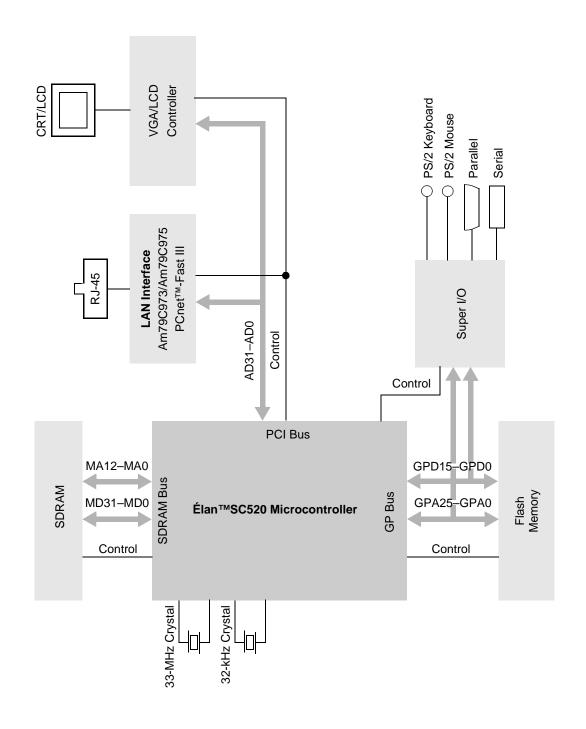

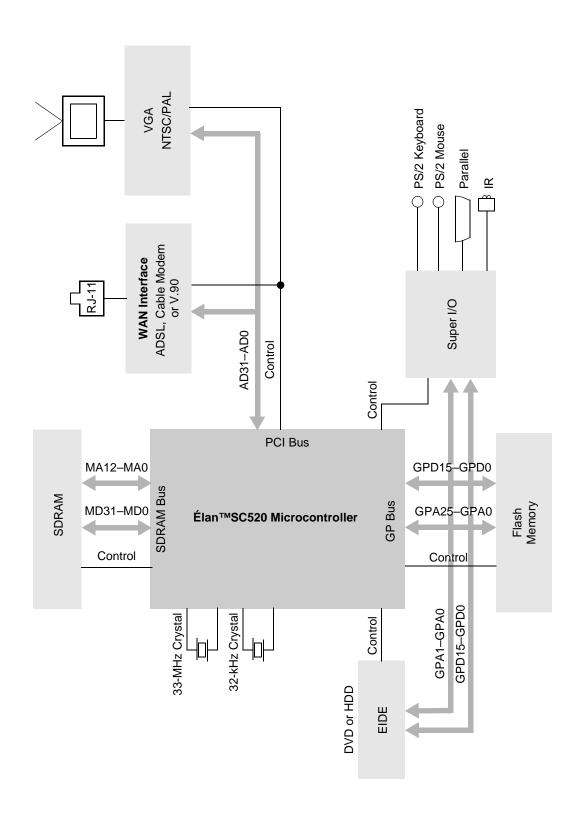

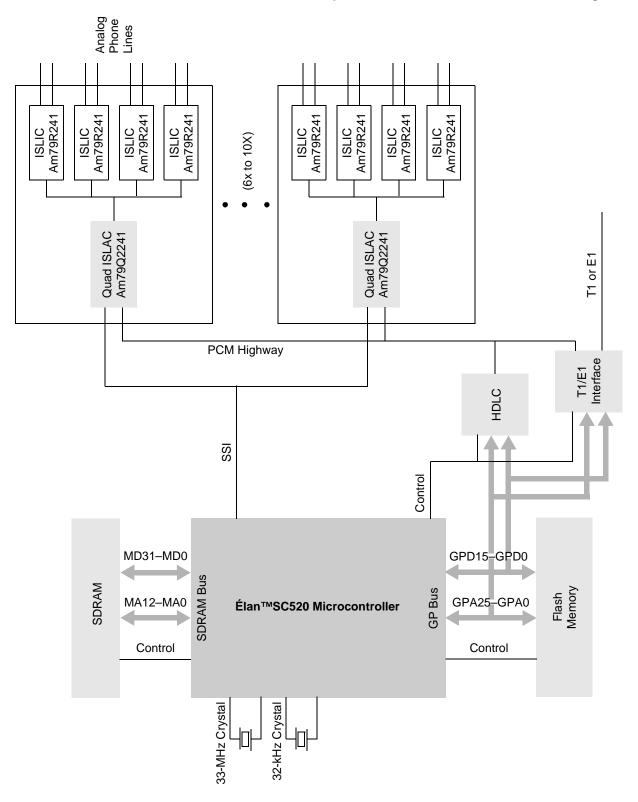

| CHAPTER 1 | ARCHITECTURAL OVERVIEW  1.1 ÉlanSC520 Microcontroller. 1.1.1 Distinctive Characteristics  1.2 Block Diagram  1.3 Architectural Overview 1.3.1 Industry-Standard x86 Architecture 1.3.2 AMDebug™ Technology for Advanced Debugging 1.3.3 Industry-Standard PCI Bus Interface. 1.3.4 High-Performance SDRAM Controller 1.3.5 ROM/Flash Controller 1.3.6 Flexible Address-Mapping 1.3.7 Easy-to-Use General-Purpose (GP) Bus Interface 1.3.8 Clock Generation 1.3.9 Integrated Peripherals 1.3.10 JTAG Boundary Scan Test Interface 1.3.11 System Testing and Debugging Features  1.4 Applications | 1-1<br>1-1<br>1-1<br>1-2<br>1-4<br>1-4<br>1-5<br>1-5<br>1-5<br>1-6<br>1-7<br>1-7<br>1-8<br>1-8 |

|           | 1.4.1       Smart Residential Gateway         1.4.2       Thin Client         1.4.3       Digital Set Top Box         1.4.4       Telephone Line Concentrator                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 1-8<br>. 1-9                                                                                 |

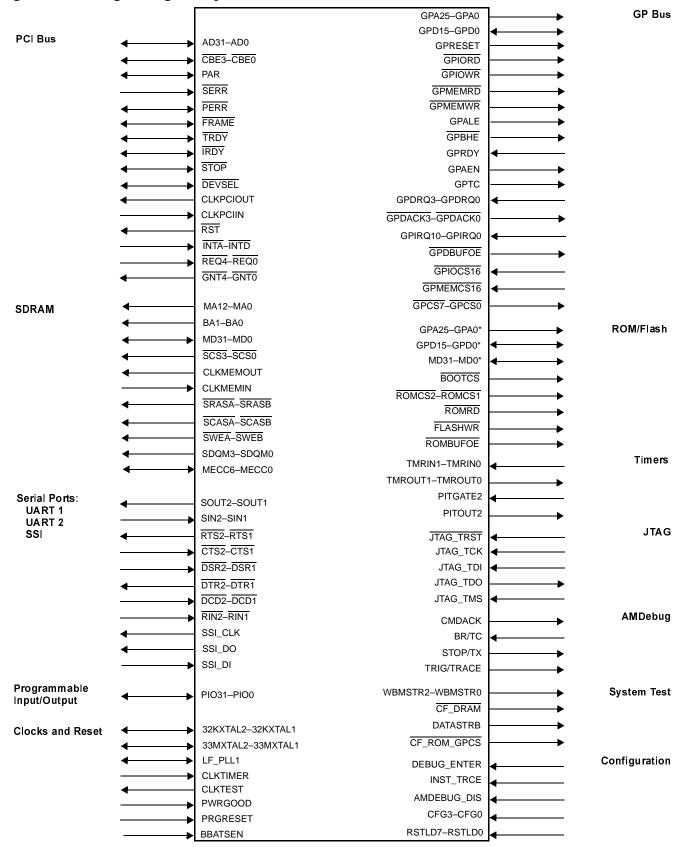

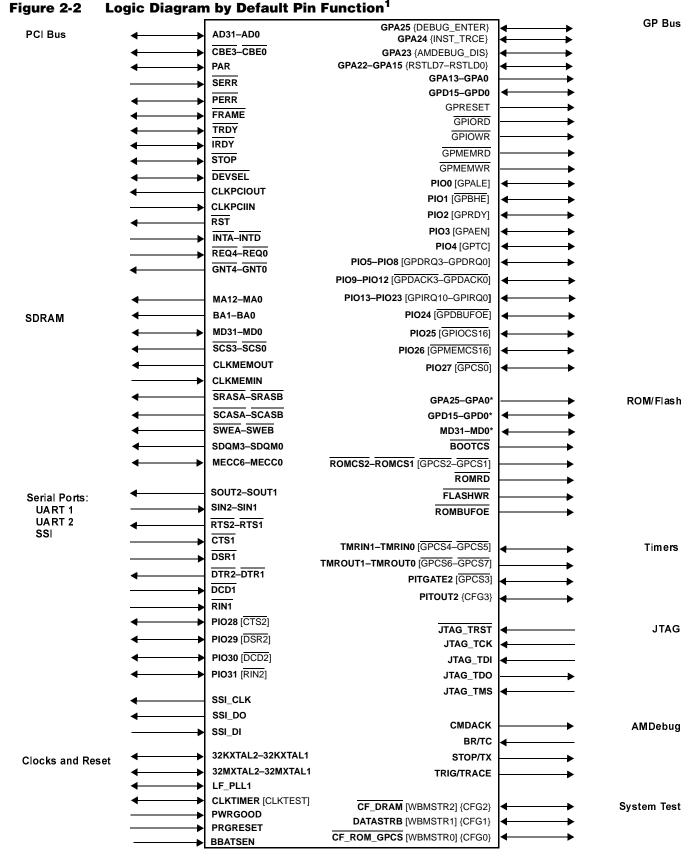

| CHAPTER 2 | PIN INFORMATION 2.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 2-1                                                                                          |

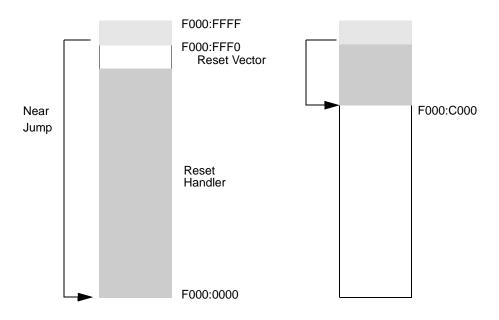

| CHAPTER 3 | SYSTEM INITIALIZATION  3.1 Overview  3.1.1 Native Embedded Initialization Sequence  3.1.2 BIOS Initialization Sequence  3.1.3 Memory-Mapped Configuration Region (MMCR)  3.1.4 Reset Event  3.1.5 Reset Vector and Reset Segment  3.2 Configuring the SDRAM Controller  3.3 Identifying the CPU Core  3.4 Setting the CPU Speed  3.5 Configuring External GP Bus Devices  3.6 Configuring the Pin Multiplexing.  3.7 Configuring the Programmable Address Region (PAR) Registers  3.7.1 Specifying Pages and Regions                                                                            | . 3-3<br>. 3-4<br>. 3-5<br>. 3-6<br>. 3-7<br>. 3-7<br>. 3-8                                    |

|           |     | 3.7.2                                     | Address                                                                                                                                                                        | Region Attributes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-12                                                                                    |

|-----------|-----|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|           |     |                                           | 3.7.2.1                                                                                                                                                                        | Write-Protect Attribute                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-12                                                                                    |

|           |     |                                           | 3.7.2.2                                                                                                                                                                        | Cacheability Control Attribute                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-12                                                                                    |

|           |     |                                           | 3.7.2.3                                                                                                                                                                        | Code Execution Attribute                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-12                                                                                    |

|           |     |                                           | 3.7.2.4                                                                                                                                                                        | Performance Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-12                                                                                    |

|           |     | 3.7.3                                     | PAR Reg                                                                                                                                                                        | gister Priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-13                                                                                    |

|           |     | 3.7.4                                     |                                                                                                                                                                                | GP Bus Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                         |

|           |     |                                           | 3.7.4.1                                                                                                                                                                        | Single Device (an A/D Converter) Using                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                         |

|           |     |                                           |                                                                                                                                                                                | One Chip Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-14                                                                                    |

|           |     |                                           | 3.7.4.2                                                                                                                                                                        | Single Device That Performs Its Own Decode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                         |

|           |     |                                           | 3.7.4.3                                                                                                                                                                        | Multiple Devices On One Chip Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-14                                                                                    |

|           |     | 3.7.5                                     | PCI Bus                                                                                                                                                                        | Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-15                                                                                    |

|           |     |                                           | 3.7.5.1                                                                                                                                                                        | VGA Controller on the PCI Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-15                                                                                    |

|           |     |                                           | 3.7.5.2                                                                                                                                                                        | Network Adapter for Remote Program Loading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-16                                                                                    |

|           |     | 3.7.6                                     | External                                                                                                                                                                       | ROM Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-17                                                                                    |

|           |     |                                           | 3.7.6.1                                                                                                                                                                        | Boot ROM Device Mapping for BIOS Shadowing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-17                                                                                    |

|           |     |                                           | 3.7.6.2                                                                                                                                                                        | Two Banks of Flash for an Execute-In-Place (XIP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2 17                                                                                    |

|           |     | 077                                       | CDDAM                                                                                                                                                                          | Operating System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                         |

|           |     | 3.7.7                                     |                                                                                                                                                                                | Regions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                         |

|           |     |                                           | 3.7.7.1                                                                                                                                                                        | Setting Up DMA Buffers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                         |

|           | 2.0 | Confin                                    | 3.7.7.2                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                         |

|           | 3.8 |                                           |                                                                                                                                                                                | nterrupt Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                         |

|           |     | 3.8.1<br>3.8.2                            |                                                                                                                                                                                | nsitive or Level-Triggered Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                         |

|           |     | 3.8.3                                     |                                                                                                                                                                                | Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                         |

|           | 2.0 |                                           |                                                                                                                                                                                | Programmable I/O Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                         |

|           |     |                                           |                                                                                                                                                                                | PCI Host Bridge and Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                         |

|           |     | -                                         | -                                                                                                                                                                              | l Peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                         |

|           |     |                                           | •                                                                                                                                                                              | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                         |

| CHAPTER 4 |     |                                           |                                                                                                                                                                                | MAPPING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-1                                                                                     |

|           |     |                                           |                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                         |

|           |     |                                           |                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                         |

|           | 4.3 | O                                         |                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4.0                                                                                     |

|           | 1.0 | •                                         |                                                                                                                                                                                | ming Fytograph Mamory Duggs, and Chin Cologta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                         |

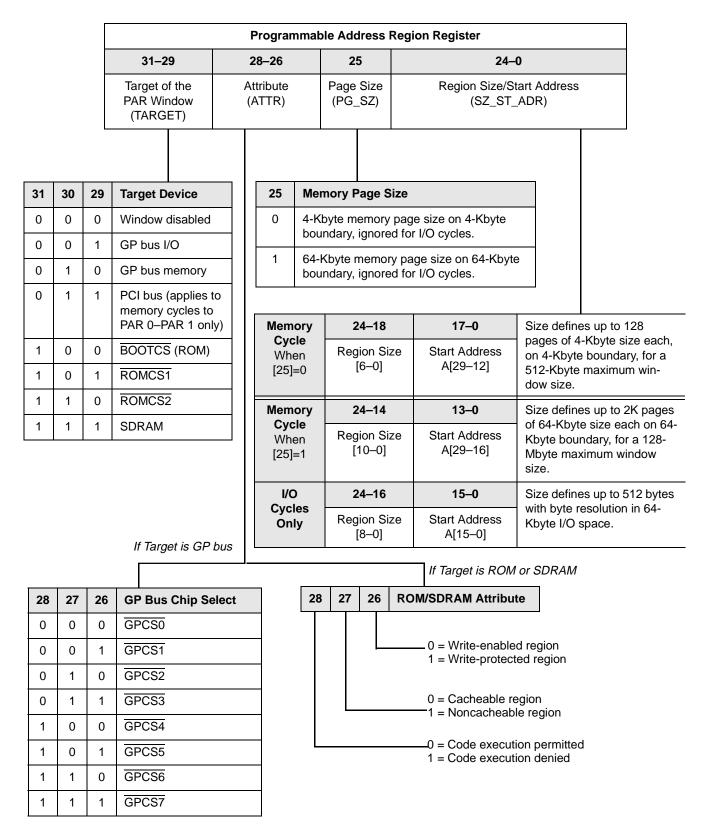

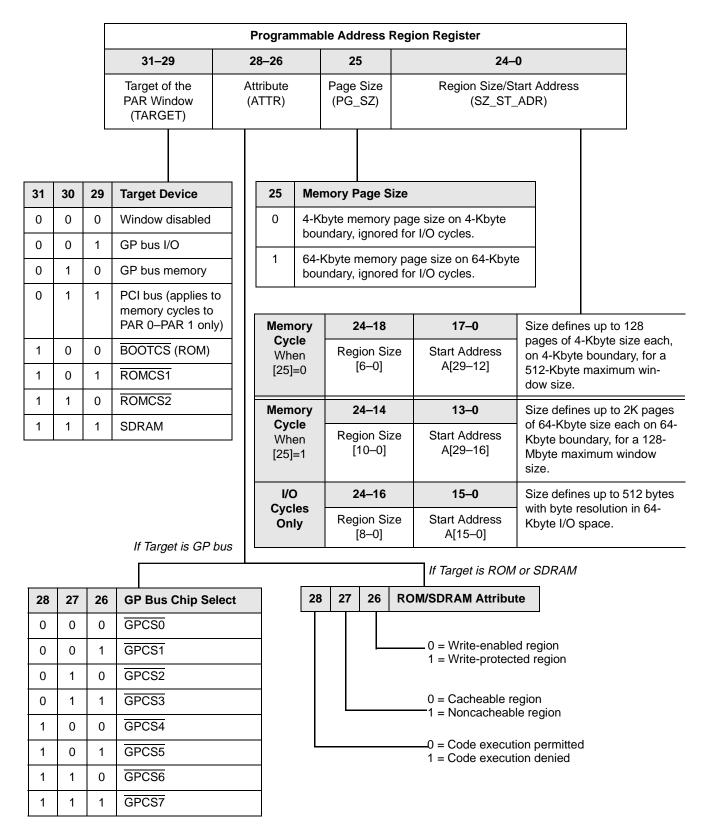

|           | 1.0 | 4.3.1                                     | Program                                                                                                                                                                        | ming External Memory, Buses, and Chip Selects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-4                                                                                     |

|           | 1.0 | 4.3.1<br>4.3.2                            | Program<br>Program                                                                                                                                                             | ming External Memory, Buses, and Chip Selects mable Address Region (PAR) Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-4<br>4-5                                                                              |

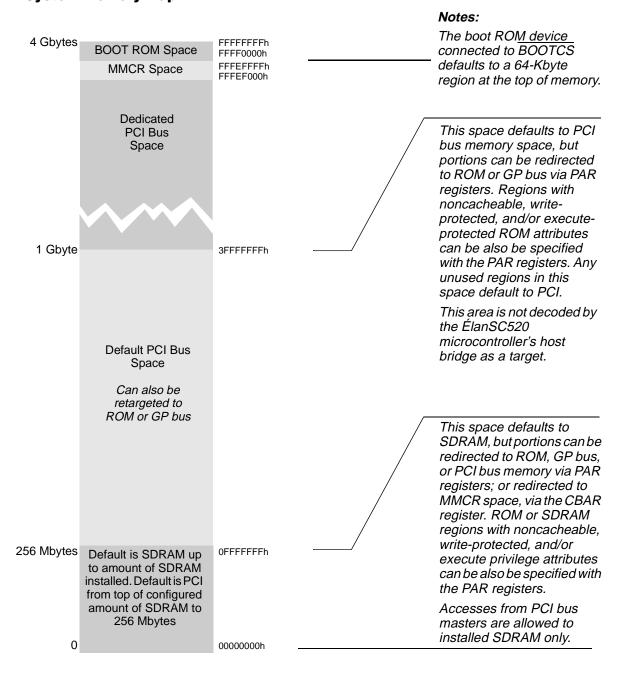

|           | 1.0 | 4.3.1                                     | Program<br>Program<br>Memory                                                                                                                                                   | ming External Memory, Buses, and Chip Selects mable Address Region (PAR) Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-4<br>4-5<br>4-7                                                                       |

|           | 1.0 | 4.3.1<br>4.3.2                            | Program<br>Program<br>Memory<br>4.3.3.1                                                                                                                                        | ming External Memory, Buses, and Chip Selects mable Address Region (PAR) Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-4<br>4-5<br>4-7<br>4-8                                                                |

|           | 1.0 | 4.3.1<br>4.3.2                            | Program<br>Program<br>Memory<br>4.3.3.1<br>4.3.3.2                                                                                                                             | ming External Memory, Buses, and Chip Selects mable Address Region (PAR) Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-4<br>4-5<br>4-7<br>4-8                                                                |

|           | 1.0 | 4.3.1<br>4.3.2                            | Program<br>Program<br>Memory<br>4.3.3.1<br>4.3.3.2<br>4.3.3.3                                                                                                                  | ming External Memory, Buses, and Chip Selects mable Address Region (PAR) Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-4<br>4-5<br>4-7<br>4-8<br>4-8                                                         |

|           |     | 4.3.1<br>4.3.2                            | Program<br>Program<br>Memory<br>4.3.3.1<br>4.3.3.2<br>4.3.3.3<br>4.3.3.4                                                                                                       | ming External Memory, Buses, and Chip Selects mable Address Region (PAR) Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-4<br>4-5<br>4-7<br>4-8<br>4-8                                                         |

|           | 1.0 | 4.3.1<br>4.3.2                            | Program<br>Program<br>Memory<br>4.3.3.1<br>4.3.3.2<br>4.3.3.3                                                                                                                  | ming External Memory, Buses, and Chip Selects mable Address Region (PAR) Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-4<br>4-5<br>4-7<br>4-8<br>4-8<br>4-9                                                  |

|           |     | 4.3.1<br>4.3.2<br>4.3.3                   | Program<br>Program<br>Memory<br>4.3.3.1<br>4.3.3.2<br>4.3.3.3<br>4.3.3.4<br>4.3.3.5                                                                                            | ming External Memory, Buses, and Chip Selects mable Address Region (PAR) Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-4<br>4-5<br>4-7<br>4-8<br>4-9<br>4-9                                                  |

|           |     | 4.3.1<br>4.3.2                            | Program Program Memory 4.3.3.1 4.3.3.2 4.3.3.3 4.3.3.4 1.3.3.5                                                                                                                 | ming External Memory, Buses, and Chip Selects mable Address Region (PAR) Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-4<br>4-5<br>4-8<br>4-8<br>4-9<br>4-9<br>4-10                                          |

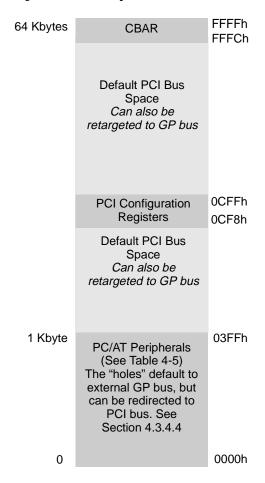

|           |     | 4.3.1<br>4.3.2<br>4.3.3                   | Program Program Memory 4.3.3.1 4.3.3.2 4.3.3.3 4.3.3.4 4.3.3.5 I/O Space 4.3.4.1                                                                                               | ming External Memory, Buses, and Chip Selects mable Address Region (PAR) Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-4<br>4-5<br>4-7<br>4-8<br>4-9<br>4-9<br>4-10<br>4-11                                  |

|           |     | 4.3.1<br>4.3.2<br>4.3.3                   | Program Program Memory 4.3.3.1 4.3.3.2 4.3.3.3 4.3.3.4 4.3.3.5  I/O Space 4.3.4.1 4.3.4.2                                                                                      | ming External Memory, Buses, and Chip Selects mable Address Region (PAR) Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-4<br>4-5<br>4-7<br>4-8<br>4-9<br>4-9<br>4-10<br>4-11                                  |

|           |     | 4.3.1<br>4.3.2<br>4.3.3                   | Program<br>Program<br>Memory<br>4.3.3.1<br>4.3.3.2<br>4.3.3.3<br>4.3.3.4<br>4.3.3.5<br>I/O Space<br>4.3.4.1<br>4.3.4.2<br>4.3.4.3                                              | ming External Memory, Buses, and Chip Selects mable Address Region (PAR) Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-4<br>4-5<br>4-8<br>4-9<br>4-9<br>4-10<br>4-11<br>4-11                                 |

|           |     | 4.3.1<br>4.3.2<br>4.3.3                   | Program<br>Program<br>Memory<br>4.3.3.1<br>4.3.3.2<br>4.3.3.3<br>4.3.3.4<br>4.3.3.5<br>I/O Space<br>4.3.4.1<br>4.3.4.2<br>4.3.4.3<br>4.3.4.4                                   | ming External Memory, Buses, and Chip Selects mable Address Region (PAR) Registers Space SDRAM Space ROM/Flash Space GP Bus Memory Space PCI Bus Memory Space Memory-Mapped Configuration Region (MMCR) Registers Space Configuration Base Address (CBAR) Register PCI Configuration Space PCI I/O Space PC/AT-Compatible I/O Peripherals Region                                                                                                                                                                                                                                      | 4-4<br>4-5<br>4-8<br>4-9<br>4-9<br>4-10<br>4-11<br>4-11                                 |

|           |     | 4.3.1<br>4.3.2<br>4.3.3                   | Program Program Memory 4.3.3.1 4.3.3.2 4.3.3.3 4.3.3.4 4.3.3.5  I/O Space 4.3.4.1 4.3.4.2 4.3.4.3 4.3.4.3                                                                      | ming External Memory, Buses, and Chip Selects mable Address Region (PAR) Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-4<br>4-5<br>4-8<br>4-9<br>4-9<br>4-10<br>4-11<br>4-12<br>4-12                         |

|           |     | 4.3.1<br>4.3.2<br>4.3.3                   | Program Program Memory 4.3.3.1 4.3.3.2 4.3.3.3 4.3.3.5 I/O Space 4.3.4.1 4.3.4.2 4.3.4.3 4.3.4.5 Configure                                                                     | ming External Memory, Buses, and Chip Selects mable Address Region (PAR) Registers Space SDRAM Space ROM/Flash Space GP Bus Memory Space PCI Bus Memory Space Memory-Mapped Configuration Region (MMCR) Registers Space Configuration Base Address (CBAR) Register PCI Configuration Space PCI Configuration Space PCI I/O Space PC/AT-Compatible I/O Peripherals Region GP Bus I/O Region ation Information                                                                                                                                                                          | 4-4<br>4-5<br>4-8<br>4-9<br>4-9<br>4-10<br>4-11<br>4-12<br>4-14                         |

|           |     | 4.3.1<br>4.3.2<br>4.3.3                   | Program Program Memory 4.3.3.1 4.3.3.2 4.3.3.3 4.3.3.5 I/O Space 4.3.4.1 4.3.4.2 4.3.4.3 4.3.4.5 Configure 4.3.5.1                                                             | ming External Memory, Buses, and Chip Selects mable Address Region (PAR) Registers Space SDRAM Space ROM/Flash Space GP Bus Memory Space PCI Bus Memory Space Memory-Mapped Configuration Region (MMCR) Registers Space Configuration Base Address (CBAR) Register PCI Configuration Space PCI Configuration Space PCI I/O Space PC/AT-Compatible I/O Peripherals Region GP Bus I/O Region ation Information Configuring ROM/Flash Space                                                                                                                                              | 4-4<br>4-5<br>4-8<br>4-9<br>4-9<br>4-10<br>4-11<br>4-12<br>4-14<br>4-14                 |

|           |     | 4.3.1<br>4.3.2<br>4.3.3                   | Program Program Memory 4.3.3.1 4.3.3.2 4.3.3.3 4.3.3.5 I/O Space 4.3.4.1 4.3.4.2 4.3.4.3 4.3.4.5 Configure 4.3.5.1 4.3.5.2                                                     | ming External Memory, Buses, and Chip Selects mable Address Region (PAR) Registers Space SDRAM Space ROM/Flash Space GP Bus Memory Space PCI Bus Memory Space Memory-Mapped Configuration Region (MMCR) Registers Space Configuration Base Address (CBAR) Register PCI Configuration Space PCI I/O Space PC/AT-Compatible I/O Peripherals Region GP Bus I/O Region ation Information Configuring ROM/Flash Space Configuring SDRAM Address Space                                                                                                                                      | 4-4<br>4-5<br>4-8<br>4-9<br>4-9<br>4-10<br>4-11<br>4-12<br>4-14<br>4-14                 |

|           |     | 4.3.1<br>4.3.2<br>4.3.3                   | Program Program Memory 4.3.3.1 4.3.3.2 4.3.3.3 4.3.3.4 4.3.3.5  I/O Space 4.3.4.1 4.3.4.2 4.3.4.3 4.3.4.5 Configure 4.3.5.1 4.3.5.2 4.3.5.3                                    | ming External Memory, Buses, and Chip Selects mable Address Region (PAR) Registers Space SDRAM Space ROM/Flash Space GP Bus Memory Space PCI Bus Memory Space Memory-Mapped Configuration Region (MMCR) Registers Space Configuration Base Address (CBAR) Register PCI Configuration Space PCI I/O Space PCI I/O Space PC/AT-Compatible I/O Peripherals Region GP Bus I/O Region ation Information Configuring ROM/Flash Space Configuring SDRAM Address Space Configuring GP Bus Peripheral Space                                                                                    | 4-4<br>4-5<br>4-8<br>4-9<br>4-9<br>4-10<br>4-11<br>4-12<br>4-14<br>4-14                 |

|           |     | 4.3.1<br>4.3.2<br>4.3.3                   | Program Program Memory 4.3.3.1 4.3.3.2 4.3.3.3 4.3.3.5 I/O Space 4.3.4.1 4.3.4.2 4.3.4.3 4.3.4.5 Configure 4.3.5.1 4.3.5.2                                                     | ming External Memory, Buses, and Chip Selects mable Address Region (PAR) Registers Space SDRAM Space ROM/Flash Space GP Bus Memory Space PCI Bus Memory Space Memory-Mapped Configuration Region (MMCR) Registers Space Configuration Base Address (CBAR) Register PCI Configuration Space PCI I/O Space PC/AT-Compatible I/O Peripherals Region GP Bus I/O Region ation Information Configuring ROM/Flash Space Configuring SDRAM Address Space Configuring GP Bus Peripheral Space Configuring the ÉlanSC520 Microcontroller                                                        | 4-4<br>4-5<br>4-8<br>4-9<br>4-9<br>4-11<br>4-11<br>4-14<br>4-14<br>4-14                 |

|           |     | 4.3.1<br>4.3.2<br>4.3.3                   | Program Program Memory 4.3.3.1 4.3.3.2 4.3.3.3 4.3.3.4 4.3.3.5 I/O Space 4.3.4.1 4.3.4.2 4.3.4.3 4.3.4.4 4.3.4.5 Configure 4.3.5.1 4.3.5.2 4.3.5.3 4.3.5.4                     | ming External Memory, Buses, and Chip Selects mable Address Region (PAR) Registers Space SDRAM Space ROM/Flash Space GP Bus Memory Space PCI Bus Memory Space Memory-Mapped Configuration Region (MMCR) Registers Space Configuration Base Address (CBAR) Register PCI Configuration Space PCI I/O Space PCI I/O Space PC/AT-Compatible I/O Peripherals Region GP Bus I/O Region ation Information Configuring ROM/Flash Space Configuring SDRAM Address Space Configuring GP Bus Peripheral Space Configuring the ÉlanSC520 Microcontroller for Windows® Compatibility               | 4-4<br>4-5<br>4-8<br>4-9<br>4-9<br>4-10<br>4-11<br>4-12<br>4-14<br>4-14<br>4-14         |

|           |     | 4.3.1<br>4.3.2<br>4.3.3<br>4.3.4          | Program Program Memory 4.3.3.1 4.3.3.2 4.3.3.3 4.3.3.4 4.3.3.5  I/O Space 4.3.4.1 4.3.4.2 4.3.4.3 4.3.4.5 Configure 4.3.5.1 4.3.5.2 4.3.5.3 4.3.5.4  4.3.5.5                   | ming External Memory, Buses, and Chip Selects mable Address Region (PAR) Registers Space SDRAM Space ROM/Flash Space GP Bus Memory Space PCI Bus Memory Space Memory-Mapped Configuration Region (MMCR) Registers Space Configuration Base Address (CBAR) Register PCI Configuration Space PCI I/O Space PC/AT-Compatible I/O Peripherals Region GP Bus I/O Region ation Information Configuring ROM/Flash Space Configuring SDRAM Address Space Configuring GP Bus Peripheral Space Configuring the ÉlanSC520 Microcontroller for Windows® Compatibility Configuring PCI Bus Devices | 4-4<br>4-7<br>4-8<br>4-9<br>4-9<br>4-10<br>4-11<br>4-12<br>4-14<br>4-14<br>4-14<br>4-15 |

|           |     | 4.3.1<br>4.3.2<br>4.3.3                   | Program Program Memory 4.3.3.1 4.3.3.2 4.3.3.3 4.3.3.4 4.3.3.5 I/O Space 4.3.4.1 4.3.4.2 4.3.4.3 4.3.4.4 4.3.4.5 Configur 4.3.5.1 4.3.5.2 4.3.5.3 4.3.5.4 4.3.5.5 Interrupts   | ming External Memory, Buses, and Chip Selects mable Address Region (PAR) Registers Space SDRAM Space ROM/Flash Space GP Bus Memory Space PCI Bus Memory Space Memory-Mapped Configuration Region (MMCR) Registers Space Configuration Base Address (CBAR) Register PCI Configuration Space PCI I/O Space PC/AT-Compatible I/O Peripherals Region GP Bus I/O Region ation Information Configuring ROM/Flash Space Configuring SDRAM Address Space Configuring GP Bus Peripheral Space Configuring the ÉlanSC520 Microcontroller for Windows® Compatibility Configuring PCI Bus Devices | 4-4<br>4-5<br>4-8<br>4-9<br>4-9<br>4-10<br>4-11<br>4-12<br>4-14<br>4-14<br>4-15<br>4-15 |

|           |     | 4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5 | Program Program Memory 4.3.3.1 4.3.3.2 4.3.3.3 4.3.3.4 4.3.3.5 I/O Space 4.3.4.1 4.3.4.2 4.3.4.3 4.3.4.5 Configure 4.3.5.1 4.3.5.2 4.3.5.3 4.3.5.4 4.3.5.5 Interrupts Software | ming External Memory, Buses, and Chip Selects mable Address Region (PAR) Registers Space SDRAM Space ROM/Flash Space GP Bus Memory Space PCI Bus Memory Space Memory-Mapped Configuration Region (MMCR) Registers Space Configuration Base Address (CBAR) Register PCI Configuration Space PCI I/O Space PC/AT-Compatible I/O Peripherals Region GP Bus I/O Region ation Information Configuring ROM/Flash Space Configuring SDRAM Address Space Configuring GP Bus Peripheral Space Configuring the ÉlanSC520 Microcontroller for Windows® Compatibility Configuring PCI Bus Devices | 4-44-54-74-84-94-94-104-114-124-144-144-154-164-174-17                                  |

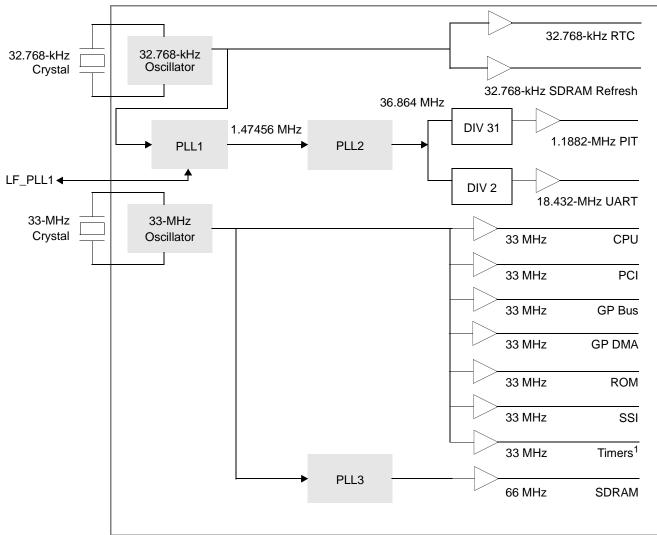

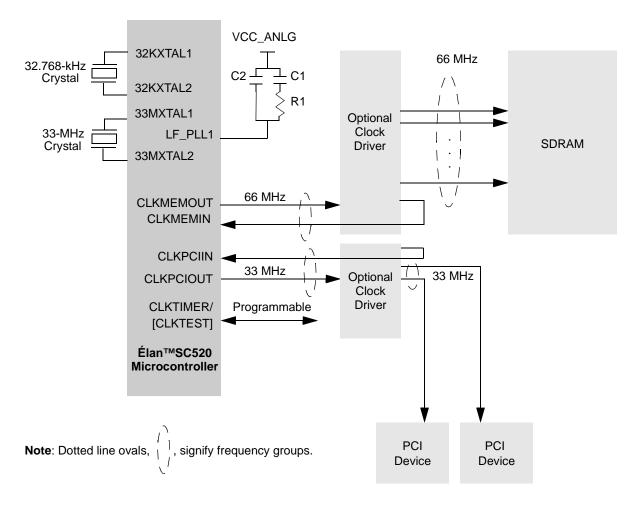

| CHAPTER 5        |     |           | NERATION AND CONTROL                          | 5-1   |

|------------------|-----|-----------|-----------------------------------------------|-------|

|                  |     |           | ew                                            |       |

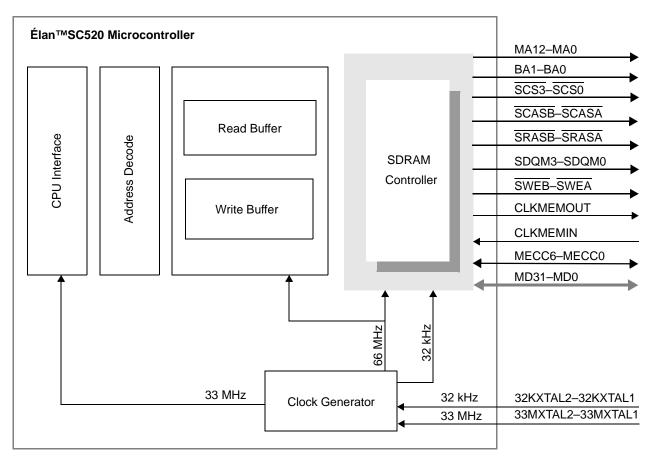

|                  |     |           | Diagram                                       |       |

|                  | 5.3 | Systen    | n Design                                      |       |

|                  |     | 5.3.1     | Clock Pin Loading                             | . 5-4 |

|                  |     | 5.3.2     | Selecting a Crystal                           | . 5-4 |

|                  |     |           | 5.3.2.1 Running the ÉlanSC520 Microcontroller |       |

|                  |     |           | at 33.333 MHz                                 |       |

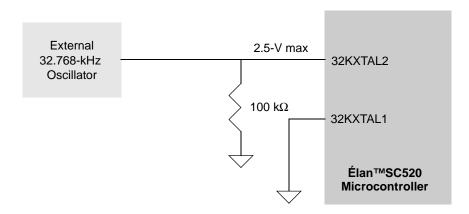

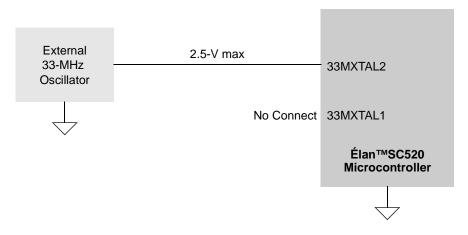

|                  |     | 5.3.3     | Bypassing Internal Oscillators                | . 5-5 |

|                  |     |           | ers                                           |       |

|                  | 5.5 |           | ion                                           |       |

|                  |     | 5.5.1     | Internal Clocks                               | . 5-7 |

|                  |     |           | 5.5.1.1 CPU                                   | . 5-7 |

|                  |     |           | 5.5.1.2 PCI Bus                               |       |

|                  |     |           | 5.5.1.3 SDRAM Controller                      |       |

|                  |     |           | 5.5.1.4 ROM/Flash Interface                   | . 5-7 |

|                  |     |           | 5.5.1.5 GP Bus                                |       |

|                  |     |           | 5.5.1.6 GP-DMA Controller                     |       |

|                  |     |           | 5.5.1.7 Programmable Interval Timer           |       |

|                  |     |           | 5.5.1.8 General-Purpose Timers                |       |

|                  |     |           | 5.5.1.9 Software Timer                        |       |

|                  |     |           | 5.5.1.10 Watchdog Timer                       |       |

|                  |     |           | 5.5.1.11 Real-Time Clock                      |       |

|                  |     |           | 5.5.1.12 UART Serial Ports                    |       |

|                  |     |           | 5.5.1.13 Synchronous Serial Interface         |       |

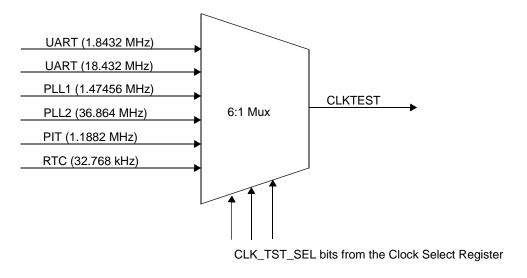

|                  |     | 5.5.2     | Using the CLKTIMER[CLKTEST] Pin               |       |

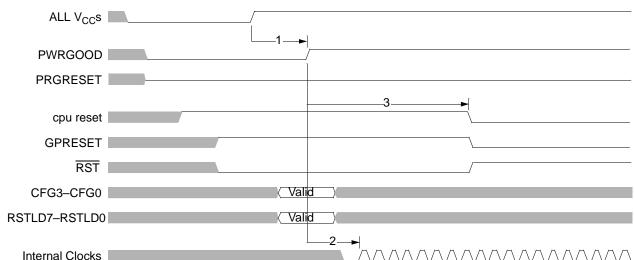

|                  | 5.6 | Initializ | ationation                                    | . 5-9 |

| <b>CHAPTER 6</b> | RES |           | NERATION                                      | 6-1   |

|                  | 6.1 |           | ew                                            |       |

|                  | 6.2 |           | Diagram                                       |       |

|                  | 6.3 | •         | n Design                                      |       |

|                  | 6.4 | _         | ers                                           |       |

|                  | 6.5 | Operat    | ion                                           |       |

|                  |     | 6.5.1     | System Reset                                  |       |

|                  |     | 6.5.2     | System Reset with SDRAM Retention             |       |

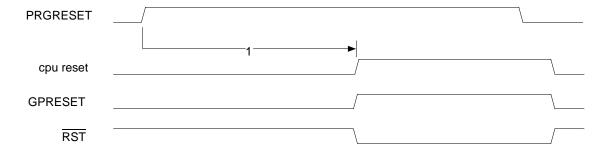

|                  |     | 6.5.3     | Soft CPU Reset                                |       |

|                  |     |           | GP Bus Reset                                  |       |

|                  |     | 6.5.5     | PCI Reset                                     |       |

|                  |     | 6.5.6     | RTC Reset                                     |       |

|                  |     | 6.5.7     | Determining Reset Sources                     |       |

|                  |     | 6.5.8     | CPU A20 Gate Support                          |       |

|                  |     | 6.5.9     | Clocking Considerations                       |       |

|                  |     | 6.5.10    | Software Considerations                       | . 6-8 |

|                  |     | 6.5.11    | Latency                                       | . 6-9 |

|                  | 6.6 | Initializ | ation                                         | . 6-9 |

| CHAPTER 7   | Am  | 5 <sub>X</sub> 86 <sup>®</sup> C | PU                 |                                                                            | 7-1  |

|-------------|-----|----------------------------------|--------------------|----------------------------------------------------------------------------|------|

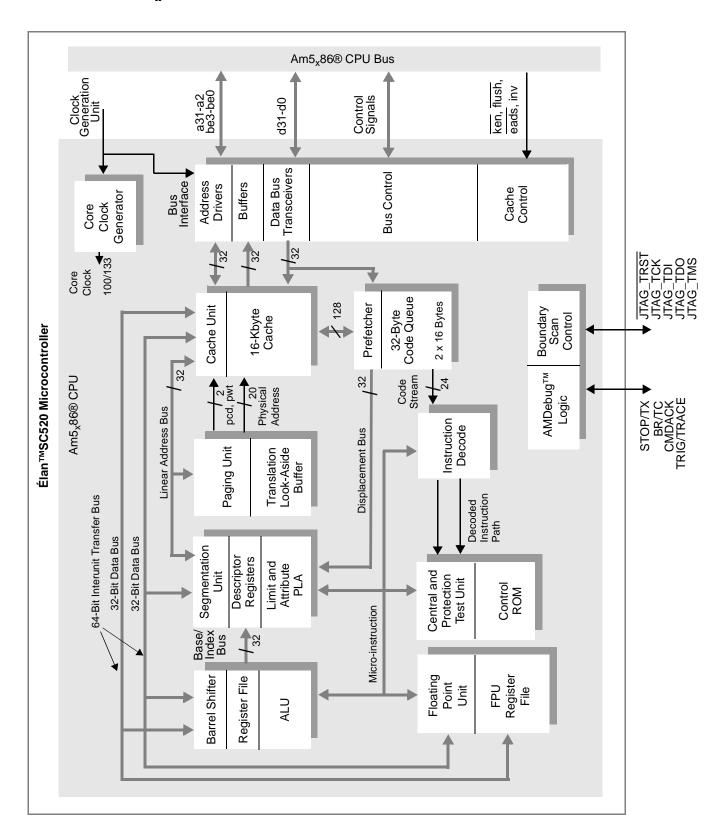

|             | 7.1 | Overvi                           | ew                 |                                                                            | 7-1  |

|             | 7.2 |                                  |                    |                                                                            |      |

|             | 7.3 |                                  |                    |                                                                            |      |

|             | 7.4 | •                                |                    |                                                                            |      |